فهرست مطالب

اصول مقایسهکننده

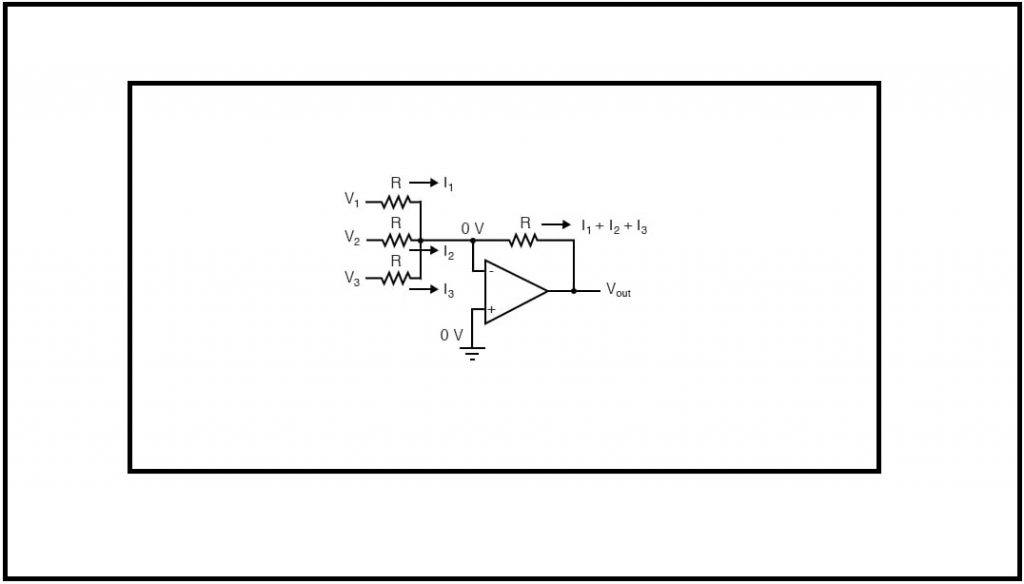

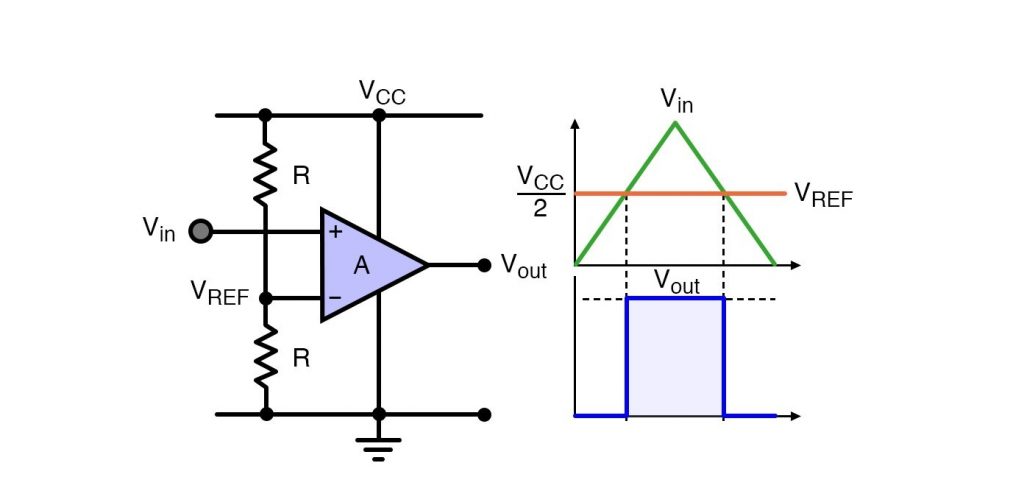

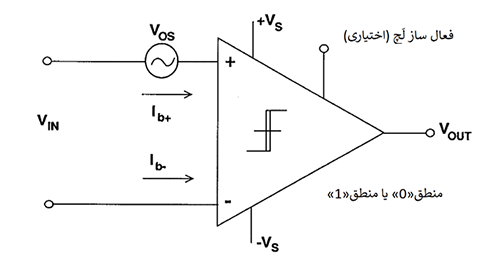

یک مقایسهکننده مشابه یک آپامپ است. دو ورودی معکوسکننده و غیرمعکوسکننده و یک خروجی دارد (شکل 1 را مشاهده کنید). اما بطور خاص برای مقایسه ولتاژهای بین دو ورودی آن طراحی شده است. بنابراین در یک مُد غیرخطی عمل میکند. مقایسهکننده حلقه باز عمل میکند، که یک ولتاژ خروجی منطقی دو حالته را تامین میکند. این دو حالت نشانگر تفاوت خالص بین دو ورودی است (از جمله اثرات ولتاژ آفست ورودی مقایسهکننده). بنابراین، اگر سیگنال ورودی غیرمعکوسکننده از سیگنال ورودی معکوسکننده فراتر برود (بعلاوه ولتاژ آفست، VOS) خروجی مقایسهکننده یک منطق «1» و در حالت مخالف یک منطق «0» خواهد بود. یک مقایسهکننده بطور معمول در کاربردهایی استفاده میشود که در آن یک سطح سیگنال متغیر با یک سطح ثابت (معمولا یک ولتاژ مرجع) مقایسه میشود. از آنجاییکه یک مبدل آنالوگ به دیجیتال (ADC) یک بیتی است، یک مقایسهکننده در تمام ADCهایی یک قطعه اصلی است. (جزییات عملکرد مقایسه کننده به عنوان یک بلوک ADC را در این آموزش مشاهده کنید)

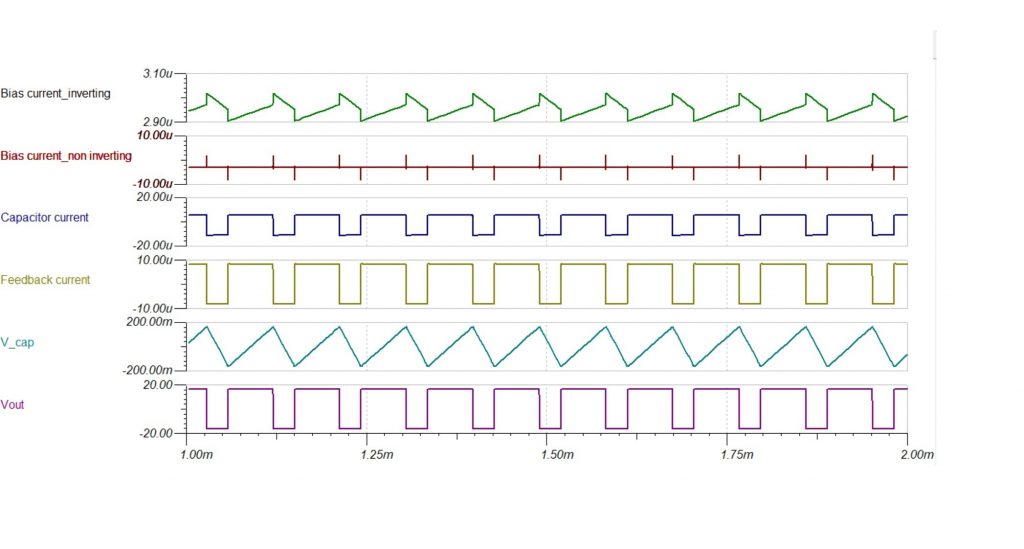

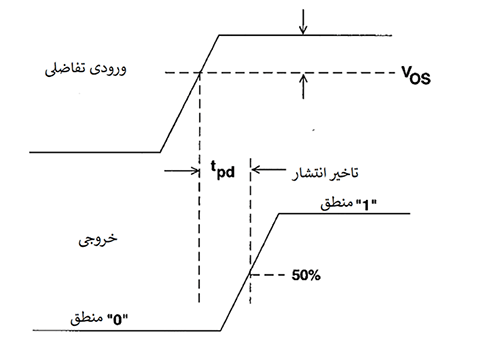

مشخصات جریان مستقیم (DC) مقایسهکننده مشابه این مشخصات برای آپامپها هستند: ولتاژ آفست ورودی، جریان تغذیه ورودی، آفست و رانش، گستره ورودی حالت مشترک، بهره، CMR، و PSR. منطق استاندارد مربوط به جریان مستقیم، زمانبندی، و مشخصات واسط مرتبط با خروجیهای مقایسهکننده هستند. مشخصه AC کلیدی مقایسهکننده تاخیر انتشار است (شکل 2 را مشاهده کنید):مدت زمانی است که خروجی پس از عبور سیگنال ورودی تفاضلی از ولتاژ آفست، برای رسیدن به نقطه 50% یک گذار نیاز دارد- هنگامیکه ورودی توسط یک موج مربعی (معمولا با دامنه 100 میلی ولت) به یک مقدار اضافه ولتاژ ورودی از پیش تعیینشده (معمولا 5 یا 10 میلیولت) تحریک میشود.

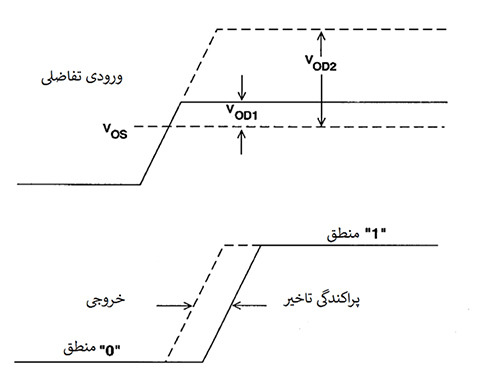

تاخیر انتشار در مقایسهکنندههای عملی هنگامیکه اضافه ولتاژ ورودی افزایش مییابد تا حدودی کاهش مییابد. این تغییر در تاخیر انتشار به عنوان تابعی از اضافه ولتاژ همانطورکه در شکل 3 نشان داده شده است پراکندگی نامیده میشود.

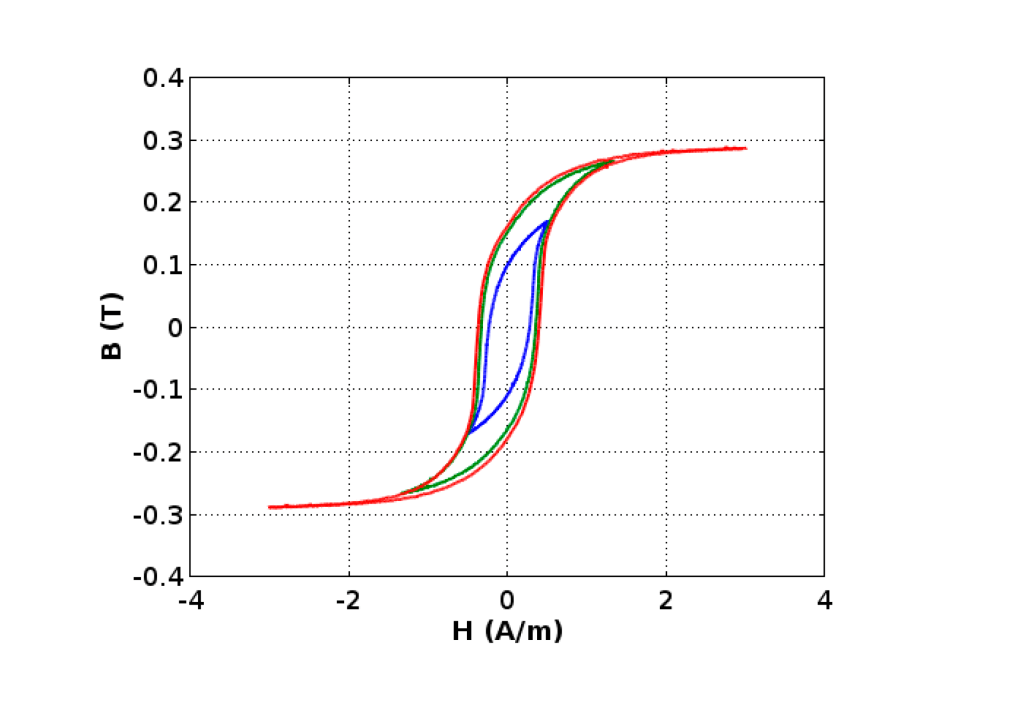

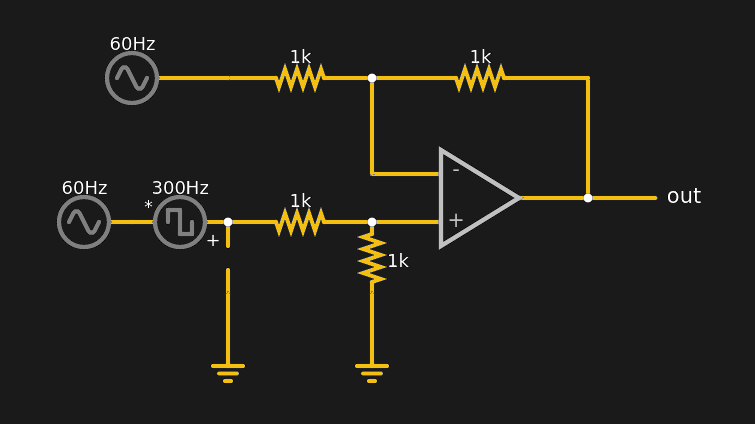

هیسترزیس مقایسه کننده

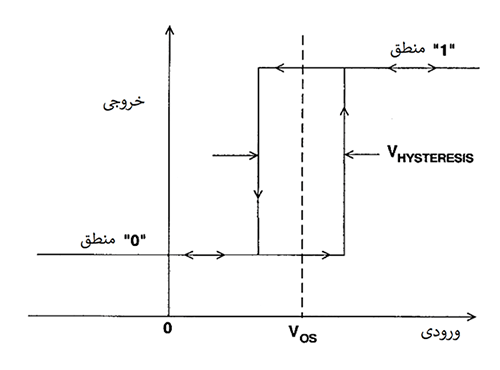

اضافه شدن هیسترزیس به تابع انتقال یک مقایسهکننده، که با استفاده از یک فیدبک مثبت کوچک انجام میشود، اغلب در محیط نویزدار، یا در جایی مفید است که سیگنال ورودی در آستانه کلیدزنی (سوئیچینگ) یا نزدیک آن است و تغییر پیوسته بین حالتها برای مقایسهکننده نامطلوب است. این امر هنگامی برقرار است که یک ورودی به آرامی در حال تغییر با یک سطح DC مقایسه میشود. نویز میتواند سبب شود خروجی دفعات بسیاری بین سطوح خروجی تغییر کند. تابع انتقال برای یک مقایسهکننده با هیسترزیس در شکل 4 نشان داده شده است.

اگر ولتاژ ورودی از جهت منفی به آستانه کلیدزنی (VOS) نزدیک شود، هنگامیکه ورودی ازVH/2 + VOS عبور میکند مقایسهکننده از یک «0» به یک «1» تغییر خواهدکرد. هم اکنون آستانه کلیدزنی «جدید»/2 VOS –VH میشود. خروجی مقایسهکننده تا زمانیکه آستانه از 2/ VOS – VH در جهت مثبت عبور داده شود در یک حالت «1» باقی خواهد ماند. نویز ورودی متمرکزشده حول VOS موجب تغییر حالت مقایسهکننده نخواهدشد مگر اینکه از ناحیه محدودشده به VOS ± VH/2 تجاوز کند.

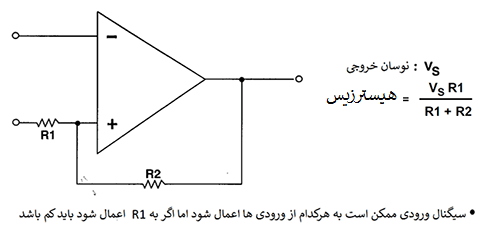

هیسترزیس میتواند با دو مقاومت اجرا شود (شکل 5 را مشاهده کنید)، و مقدار هیسترزیس متناسب با نسبت مقاومتها است. ورودی سیگنال به مقایسهکننده ممکن است به ورودی معکوسکننده یا غیرمعکوسکننده اعمال شود، اما اگر به ورودی معکوسکننده شود امپدانس منبع آن باید به اندازه کافی کم باشد بطوری که اثر قابل توجهی بررویR1 داشته باشد (البته اگر امپدانس منبع به اندازه کافی قابل پیشبینی باشد، ممکن است به عنوان R1 بکاربرده شود).

اگر ولتاژ قطع در بین دو ولتاژ خروجی مقایسهکننده باشد ( همانند حالت با منبع تغذیه متقارن و یک مرجع زمین) سپس شناساگر هیسترزیس آستانه مثبت و منفی را با فاصله یکسان از ولتاژ قطع جابجا خواهد کرد، اما اگر نقطه قطع به یکی از خروجیها نزدیکتر از دیگری باشد آستانهها بصورت نامتقارن حول نقطه قطع قرار خواهندگرفت.

برای محاسبه هیسترزیس، فرض میکنیم ولتاژهای خروجی مقایسهکننده به ترتیب VP و VN هستند. ولتاژ نقطه قطع مقایسهکننده VTP است. آستانه منفی برابر است با:

آستانه منفی =[katex]\frac{(R1+R2) V_{TP}-R1 V_{N}}{R2} [/katex] معادله 1

ولتاژ آستانه مثبت برابر است با:

آستانه مثبت =[katex]\frac{(R1+R2) V_{TP}-R1 V_{P}}{R2} [/katex] معادله 2

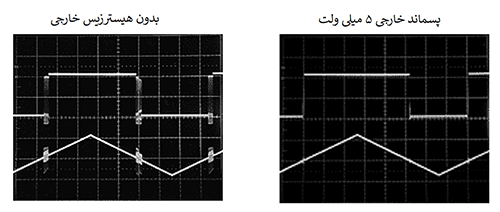

مثالی از اینکه چگونه یک هیسترزیس خارجی پاسخ مقایسهکننده را بهبود میبخشد در شکل.6 نشان داده شده است.

مشکلی که با هیسترزیس خارجی ایجاد میشود این است که ولتاژ خروجی به ولتاژ تغذیه و بارگذاری بستگی دارد. این بدین معنی است که ولتاژ هیسترزیس میتواند کاربرد به کاربرد تغییر کند؛ اگرچه این موضوع بر دقت اثر میگذارد، اما یک مشکل جدی نیست، زیرا هیسترزیس معمولا کسر بسیار کوچکی از گستره است و دقت میتواند یک حاشیه امنیت دو یا سه برابر (یا بیشتر) آنچه ممکن است محاسبه شود را تحمل کند. جاروب در تعداد کمی از مقایسهکنندهها میتواند به اطمینان در حاشیه امنیت کمک کند. از مقاومتهای سیمپیچ برای فیدبک استفاده نکنید؛ ظرفیت القا مغناطیسی آنها میتواند موضوع را بدتر کند.

فراموش نکنید اضافه کردن هیسترزیس اضافی به یک مقایسهکننده همچنین دقت موثر مقایسهکنندهها را کاهش میدهد. حداقل سیگنال تفکیکپذیری معادل تفاوت ولتاژهای آستانه، VP – VN است.

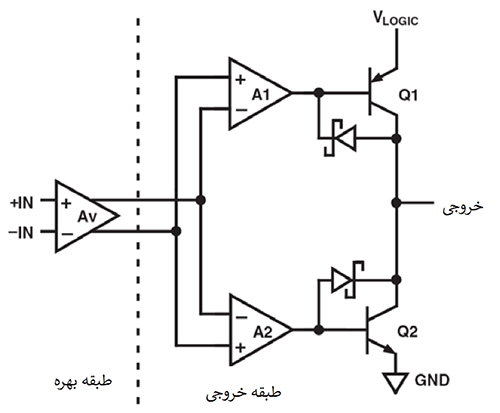

برخی مقایسهکنندهها هیسترزیس ذاتی دارند به عنوان مثال AD790 (شکل 7 را مشاهده کنید). ولتاژ هیسترزیس نامی 500 میکرو ولت است. البته میتوان با اعمال هیسترزیس خارجی این موضوع را نادیده گرفت.

AD790 مزیت دیگری نیز دارد. منابع موجود در سمت ورودی (آنالوگ) ضرورتا منابع موجود در خروجی نیستند. نوسان خروجی از VLOGIC تا زمین است. منابع ورودی میتوانند 15± تا 5+ ولت و زمین باشند.

خروجی مقایسهکننده کلکتور باز (منطق TTL) یا درین باز (منطق CMOS) کاملا متداول است. این موضوع تعامل با هر سطح منطقی مناسب را برای مداربندی بعدی امکانپذیر میسازد. توجه داشته باشید که حداکثر ولتاژ خروجی مجاز باید رعایت شود، اما این مسیله معمولا موضوع خیلی بزرگی نیست.

مقایسهکنندههای پنجرهای

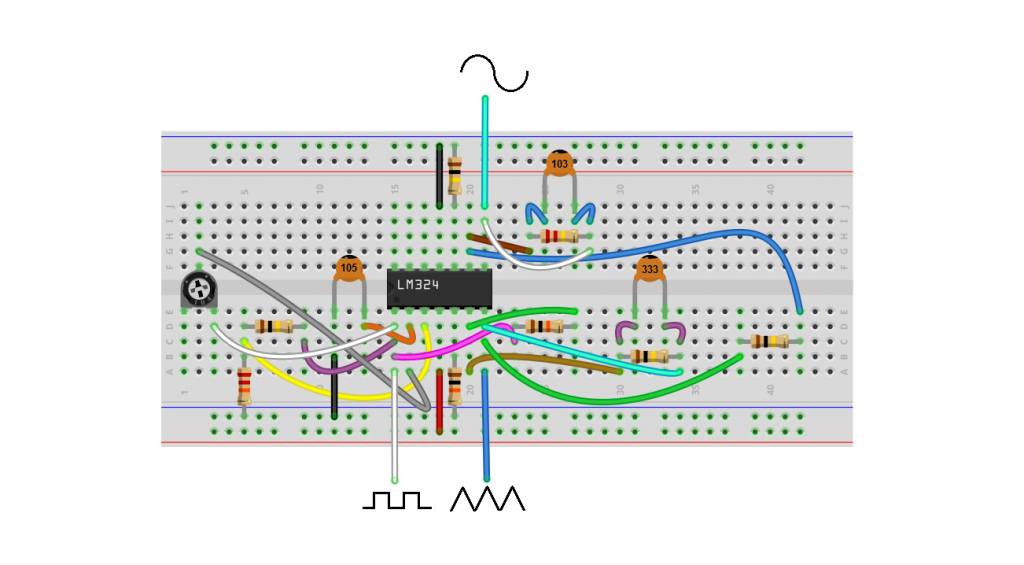

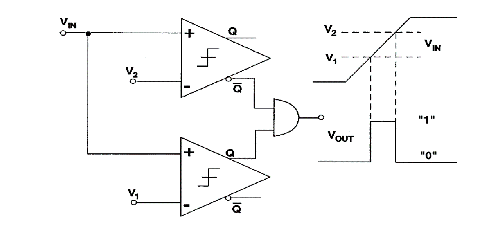

یک مقایسهکننده پنجرهای از کاربرد دو مقایسهکننده با ولتاژهای مرجع مختلف و ولتاژ ورودی مشترک استفاده میکند. ارتباط مقایسه کننده و منطق چنان است که سطح منطق خروجی نهایی هنگام واقع شدن سیگنال ورودی بین دو ولتاژ مرجع همانند شکل 8 است.

عملکرد فعالساز لچ

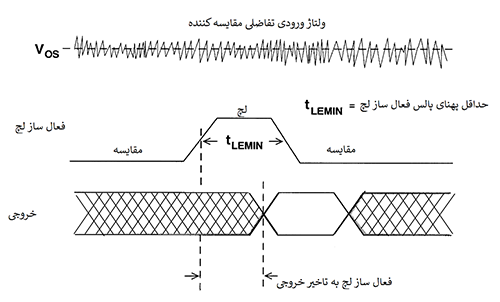

بسیاری از مقیاسکنندهها یک لَچ داخلی دارند. سیگنال فعالساز لَچ دو حالت دارد: مقایسه ( ردیابی) و لَچ (نگه داشتن). وقتی سیگنال فعالساز لَچ در حالت مقایسه است، خروجی مقایسهکننده بطور پیوسته به علامت سیگنال ورودی تفاضلی خالص پاسخ میدهد. هنگام گذار سیگنال فعالساز لَچ به حالت لَچ، خروجی مقایسهکننده، بسته به علامت سیگنال ورودی تفاضلی در لحظه گذار به منطق «1» یا منطق «0» میرود (در این نقطه؛ ما زمان نگهداری و تنظیم، همچنین تاخیر انتشار خروجی مرتبط با عملکرد فعالساز لَچ را نادیده میگیریم). اگرچه بسیاری از مقایسهکنندهها یک تابع فعالساز لَچ دارند، آنها اغلب تنها در حالت مقایسه بکاربرده میشوند.

عملکرد فعالساز لَچ بطورخاص در کاربردهای مبدل آنالوگ به دیجیتال مفید است زیرا امکان ثبت تصمیم را در یک لحظه مشخص به مقایسهکننده می دهد. مبدلهای لحظهای از بسیاری مقایسهکنندههای موازی ساخته میشوند که یک خط فعالساز لَچ مشترک دارند و از این مفهوم استفاده میکنند. زمانبندی معمول مربوط به تابع فعالساز لچ در شکل 9 نشان داده شده است.

تاخیر بین اعلان فعالساز لَچ و 50% نقطه نوسان منطق خروجی به عنوان فعال کردن لچ برای تاخیر در خروجی نامیده میشود. این تاخیر ممکن است برای خروجیهای مثبت یا منفی متفاوت باشد. دیگر مشخصه کلیدی مرتبط با عملکرد فعالساز لَچ حداقل پهنای پالس فعالساز لَچ مجاز است. این مشخصه حداکثر فرکانسی را مشخص میکند که مقایسهکننده میتواند در آن بکار برده شود.

کاربرد مقایسهکنندههای سریع به دلیل بهره بالا و پهنای باند آنها تا حدودی سخت است. کاربرد مناسب طرح سرعت بالا، زمین کردن، جداکردن و مسیریابی هنگام استفاده از مقایسهکنندهها الزامی است. بزرگترین مشکل تمایل آنها به نوسان است هنگامیکه سیگنال ورودی بسیار نزدیک یا برابر آستانه کلیدزنی است. همچنین این موضوع میتواند هنگامیکه یک سیگنال کُند با یک مرجع جریان مستقیم مقایسه میشود، رخ دهد. بطورکلی هیسترزیس و استفاده از پالس فعالساز لَچ باریک به این شرایط کمک خواهندکرد. مقایسهکنندههای خروجی TTL یا CMOS به دلیل نوسانات خروجی بزرگ و لبههای تند احتمالا بیشتر از نوع ECL نوسان میکنند، که اغلب با جهشهای جریان منبع تغذیه هنگامیکه خروجی تغییر حالت میدهد ترکیب میشوند. این موضوع میتواند به شکل نویز به ورودی بازخورد داده شود.

برای مشاهده سایر نوشتارهای مربوط به الکترونیک و مخابرات، اینجا کلیک کنید!

مترجم: فاطمه محمدی بهبهانی