فلیپ فلاپ JK شباهت زیادی به فلیپ فلاپ SR دارد. اما هنگامی که سطح هر دو ورودی J و K پایین است، هیچ تغییری در وضعیت فلیپ فلاپ رخ نمیدهد.

مدار فلیپ فلاپ NAND S-R، مزیتهای خیلی زیادی دارد و در مدارات منطقی ترتیبی به وفور استفاده میشود. اما دارای دو مشکل اساسی در سوییچینگ میباشد:

- از حالت S=0 و R=0 (S=R=0) باید اجتناب شود.

- اگر SET یا RESET تغییر وضعیت دهند و ورودی EN در سطح بالا باشد، عمل ذخیره داده ممکن است به درستی صورت نگیرد.

بنابراین برای غلبه بر این دو مشکل، در فلیپ فلاپهای SR، فلیپ فلاپهای JK طراحی شدند.

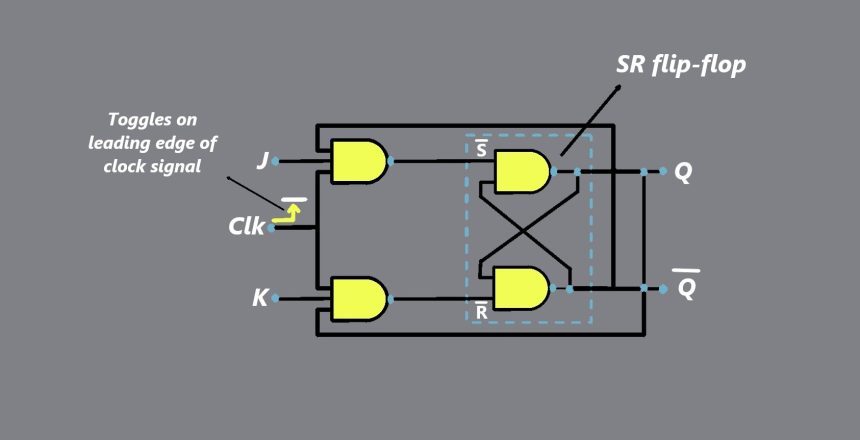

فلیپ فلاپهای JK که در تصویر بالا نشان داده شده، پرکاربردترین نوع فلیپ فلاپمیباشد و به نوعی یک مدار فلیپ فلاپ یونیورسال محسوب میشود. دو ورودی این فلیپ فلاپ با نامهای J و K مشخص شده اند. که اول نام و نام خانوادگی سازندهی آن Jack Kilby هستند.

عملکرد ترتیبی فلیپ فلاپ JK دقیقا شبیه به فلیپ فلاپ SR با همان پایههای ست و ریستمیباشد. تنها تفاوت در این است که فلیپ فلاپ JK هیچ حالت نامعلوم یا ممنوعهای ندارد و هر دو پایه J و K میتوانند ورودی منطقی یک را دریافت کنند.

فلیپ فلاپ JK در اصل یک فلیپ فلاپ SR دارای دروازه میباشد که مجهز به یک مدار کلاک ورودی است تا از بروز حالات خروجی غیرقابل قبول که در فلیپ فلاپ SR هنگامی که هر دو ورودی یک بودند، جلوگیری کند.

به دلیل وجود ورودی کلاک دار، فلیپ فلاپهای JK دارای 4 حالت ورودی ممکنمیباشند: منطق یک، منطق صفر، بدون تغییر و تغییر حالت با پالس کلاک (TOGGLE).

سمبل فلیپ فلاپهای JK به یک قفل دو حالته SR شباهت دارد. با این تفاوت که یک کلاک ورودی نیز به آن افزوده شدهاست.

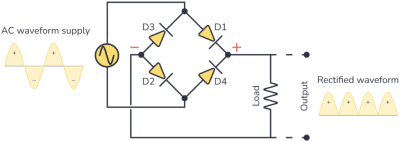

مدار پایه و شماتیک فلیپ فلاپ JK

هر دو ورودیهای S و R فلیپ فلاپهای SR یا دو ورودی به نام J و K جایگزین شده اند. به عبارتی دیگر S=J و K=R میباشد.

در فلیپ فلاپ JK، دو ورودی دروازههای AND و SR دو حالته با گیتهای NAND که 3 ورودی دارند، جایگزین شدهاند و یکی از ورودیهای فلیپ فلاپ SR به خروجیهای Q و Q’ متصل شده. این اتصال ضربدری فلیپ فلاپ SR اجازه میدهد تا حالت غیرقابل قبول S=1 و R=1 برای عملکرد TOGGLE مورد استفاده قرار بگیرد. چرا که در فلیپ فلاپ JK دو ورودی به صورت داخلی قفل شدهاند.

اگر مدار در شرایط SET قرار بگیرد، ورودی تحت تاثیر وضعیت Q’=0 گیت NAND که در پایین مدار قرار دارد، قفل خواهد شد. حال اگر فلیپ فلاپ در حالت RESET قرار بگیرد، ورودی K تحت تاثیر حالت صفر خروجی Q و از طریق گیت NAND بالایی قفل میشود. از آن جایی که Q و ’Q همواره در وضعیت متفاوتی قرار دارند، میتوانیم از آنها برای کنترل ورودی استفاده کنیم. هنگامی که هر دو رودی J و K برابر با منطق یک باشند، فلیپ فلاپ JK به صورتی که در جدول ارزشی زیر نشان داده شده به حالت TOGGLE فرومی رود.

|

|

کلاک

|

ورودی

|

خروجی

|

|

||

|---|---|---|---|---|---|---|

|

مشابه قفل SR

|

Clk

|

J

|

K

|

Q

|

--Q

|

توضیحات

|

|

X

|

0

|

0

|

1

|

0

|

هیچ تغییری در حافظه رخ نمیدهد

|

|

|

X

|

0

|

0

|

0

|

1

|

||

|

پایین رونده

|

0

|

1

|

1

|

0

|

Reset Q >> 0

|

|

|

X

|

0

|

1

|

0

|

1

|

||

|

پایین رونده

|

1

|

1

|

0

|

0

|

Set Q >> 1

|

|

|

X

|

1

|

0

|

1

|

0

|

||

|

عملکرد Toggle

|

پایین رونده

|

1

|

1

|

0

|

1

|

Toggle

|

|

پایین رونده

|

1

|

1

|

1

|

0

|

||

بنابراین فلیپ فلاپ JK به طور پایه همان فلیپ فلاپ SR است. با این تفاوت که دارای فیدبکمیباشد که تنها یکی از ترمینالهای ورودی را فعالمیکند. به عبارتی دیگر، تنها RESET یا SET میتوانند در یک زمان خاص و در حالت سوییچ معمولی فعال شوند. بنابراین شرایط غیر قابل قبولی که در فلیپ فلاپ SR به وجودمیآمد، دیگر در فلیپ فلاپ JK به وجود نخواهد آمد.

به هر حال اگر هر دو ورودیهای J و K به سطح منطقی یک بروند، (J=K=1) هنگامی که کلاک ورودی در سطح بالاست، مدار در حالت TOGGLE قرارمیگیرد. چرا که خروجیها مدام تغییر حالتمیدهند. در این شرایط، فلیپ فلاپ JK همانند یک فلیپ فلاپ TOGGLE نوع T عمل میکند که هر دو ترمینالش در سطح بالا قرار گرفته. اما از آن جایی که خروجیها به ورودی فیدبک دارند، ممکن است خروجیها بین SET و RESET نوسان کنند.

در حالیکه مدار فلیپ فلاپ JK مدار بهینه سازی شده فلیپ فلاپ دارای کلاک SRمیباشد، اما به این معنا نیست که عاری از مشکل است. این فلیپ فلاپ از مشکلات زمانبندی رنج میبرد. به عنوان مثال، ممکن است Q قبل از اینکه پالس زمانبندی ورودی کلاک فرصت رفتن به وضعیت OFF را داشته باشد، تغییر وضعیت دهد.

برای جلوگیری از بروز چنین مشکلی دوره تناوب پالس زمانبندی (T) باید تا حد ممکن کوتاه باشد. ( دارای فرکانس بالایی باشد.) و از آن جایی که نیل به این مقصود در تمام فلیپ فلاپهای JK که با استفاده از گیتهای پایهای NAND و NOR ساخته شدهاند امکانپذیر نیست، فلیپ فلاپهای پیشرفتهتری که به حالت master-slave هستند و در گوشه بالارونده یا پایین رونده تحریک میشوند، ساخته شدهاند که پایدارتر میباشند.

فلیپ فلاپ مستر- اسلیو JK

فلیپ فلاپ مستر- اسلیو مشکلات زمانبندی را با استفاده از دو فلیپ فلاپ SR که به یکدیگر به صورت سری متصل شده اند، مرتفع کرده. یک فلیپ فلاپ مانند مدار مستر عملمیکند که در گوشه ی بالارونده پالس کلاک تحریکمیشود. در حالیکه فلیپ فلاپ دیگر نقش اسلیو را بر عهده گرفته که در گوشه پایین رودنه سیگنال کلاک راه اندازیمیشود. در چنین شرایطی، بخش مستر و بخش اسلیو در نیم سیکلهای متفاوتی فعال سازیمیشوند.

TTL74LS73 یک IC با دو فلیپ فلاپ JK میباشد که دو فلیپ فلاپ میتواند به صورت تکی یا به صورت مستر- اسلیو TOGGLE در آن به کار بروند. یک مدار مجتمع فلیپ فلاپ JK دیگر، قطعه 74LS107 میباشد. همچنین قطعهی 74LS109 دارای فلیپ فلاپهای JK است که در گوشهی مثبت سیگنال کلاک تحریک میشوند. در حالیکه 74LS112 در گوشهی منفی (پایین رونده) و با ورودیهای PRESENT و CLEAR تحریک میشوند.

دو فلیپ فلاپ JK در 74LS73

آیسیهای رایج فلیپ فلاپ JK

|

پارت نامبر

|

خانواده

|

توضیحات

|

|---|---|---|

|

74LS73

|

LS TTL

|

دو فلیپ فلاپ JK با پایه Clear

|

|

74LS76

|

LS TTL

|

دو فلیپ فلاپ JK با پایه Clear و Present

|

|

74LS107

|

LS TTL

|

دو فلیپ فلاپ JK با پایه Clear

|

|

4027B

|

Standard CMOS

|

دو فلیپ فلاپ JK

|

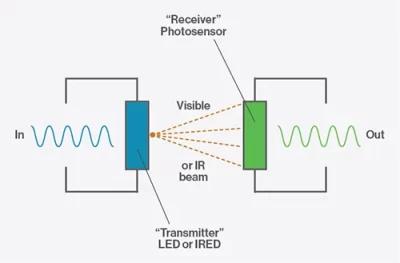

فلیپ فلاپ مستر-اسلیو در اصل دو فلیپ فلاپ SR دارای گیت میباشد که به صورت سری به یکدیگر متصل شده و اسلیو دارای پالس کلاک معکوس میباشد. خروجیها از Q و ’Q از فلیپ فلاپ اسلیو به ورودیهای مستر فیدبک دادهمیشوند و خروجیهای فلیپ فلاپ مستر به ورودی فلیپ فلاپ اسلیو متصل شدهاند.

این پیکربندی از خروجی اسلیو به مستر باعث به وجود آمدن ویژگی TOGGLE در فلیپ فلاپ JK میشود. برای درک بهتر این موضوع به شکل زیر نگاه کنید:

پیکربندی فلیپ فلاپ مستر اسلیو JK

سیگنالهای ورودی J و K به مستر متصل میباشند که شرایط ورودی را قفل کردهاست. در حالیکه ورودی (CLK) در سطح منطقی یک (بالا) خواهد بود. هنگامی که ورودی کلاک فلیپ فلاپ SR اسلیو، معکوس پالس کلاک مستر میشود، فلیپ فلاپ SR اسلیو به حالت TOGGLE فرو نمیرود و خروجیها تنها هنگامی از فلیپ فلاپ MASTER توسط فلیپ فلاپ SLAVE دیده میشوند که پالس کلاک ورودی به سطح پایین یا منطق صفر برود.

هنگامی که سطح منطقی کلاک پایین است، خروجیها از فلیپ فلاپ مستر قفل خواهند شد و تمام تغییراتی که در ورودیها رخ میدهد، نادیده گرفته میشود. حال فلیپ فلاپ اسلیو به وضعیت ورودیهایی که از بخش مستر میگذرند؛ پاسخ میدهد.

سپس اگر سیگنال کلاک مستر در گوشهی پایین رونده قرار بگیرد، ورودیهای فلیپ فلاپ SR را تغذیه کنند و در همین حین سطوح یکسانی روی خروجی اسلیو به وجود بیاید، فلیپ فلاپ تحریک پذیر با گوشه پالس به وجود خواهد آمد.

سپس مدار، دادههای ورودی را هنگامی که سیگنال کلاک HIGH است، در گوشهی پایینرونده پالس کلاک به خروجی میفرستد. به عبارتی دیگر فلیپ فلاپ JK مستر – اسلیو یک قطعه سنکرون میباشد که هماهنگ با زمانبندی سیگنال کلاک اطلاعات را از خود عبور میدهد.

در مقالهی بعدی به مولتی ویبراتورها (Multivibrators) خواهیم پرداخت که از آنها به عنوان سازندگان موج یاد میشود و برای ساخت سیگنال کلاک به منظور سوییچینگ مدارات منطقی ترتیبی به کار میروند.