مدارهای منطق ترتیبی، از فلیپ فلاپ ها به عنوان المانهای حافظه استفاده میکنند و شرایط خروجیشان وابسته به شرایط ورودی میباشد.

بر خلاف مدارهای منطقی ترکیبی که حالت شان را بر اساس سیگنال هایی که به ورودی اعمال می شود تغییر می دهند، مدارهای منطقی ترتیبی قادر هستند با در نظر گرفتن وضعیت ورودی قبلی و وضعیت فعلی شان، خروجی دلخواه را تولید کنند.

به عبارتی دیگر وضعیت خروجی یک مدار منطقی ترتیبی، تابعی از 3 وضعیت زیر است:

- ورودی فعلی

- ورودی گذشته

- خروجی گذشته

مدارهای منطق ترتیبی این 3 وضعیت را به خاطر می سپارند و در شرایط فعلیشان ثابت می مانند تا سیگنال کلاک بعدی باعث تغییر وضعیت شود و به همین دلیل است که این مدارهای را دارای حافظه میدانند.

مدارات منطق ترتیبی دارای 2 وضعیت ثابت هستند. وضعیت منطقی 0 و و ضعیت منطقی یک. این مدارها تا زمانی که پالس تحریک فرابرسد، در وضعیت فعلی خود باقی میمانند و سپس دوباره تغییر وضعیت میدهند.

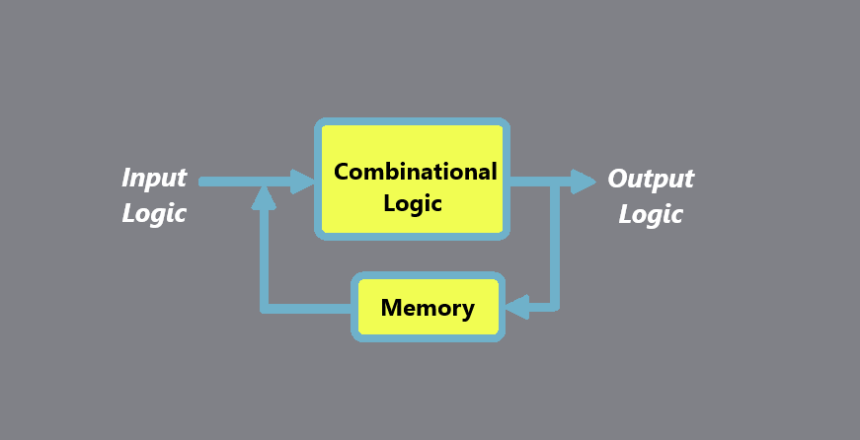

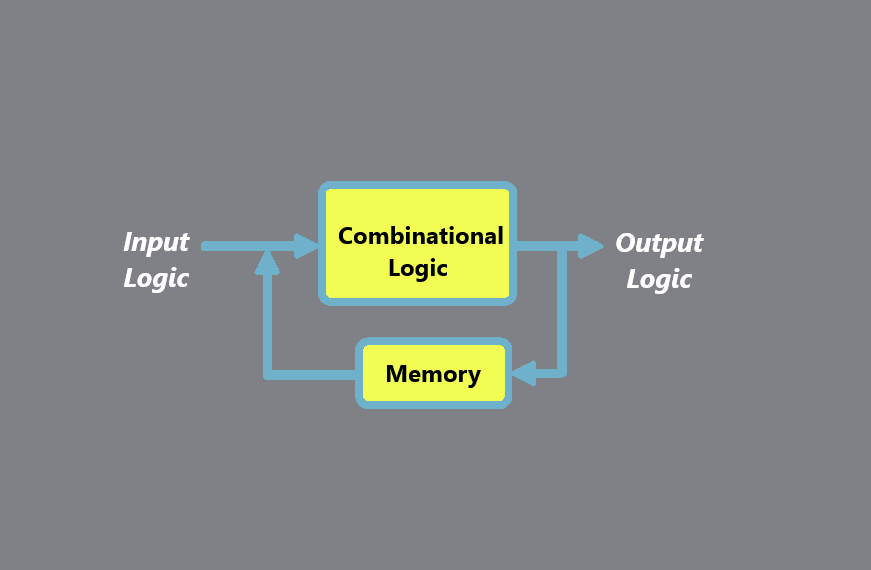

دیاگرام مدار منطقی ترتیبی

لغت “ترتیبی” به این معناست که رویدادها در یک ترتیب به خصوص رخ میدهند. سیگنال کلاک مشخص میکند چه زمانی وضعیت تغییر خواهد کرد. مدارهای ساده ترتیبی می توانند از مدارهای استاندارد دو حالته مانند: فلیپ فلاپ، شمارندهها و قفلها تشکیل شوند. این مدارهای نیز با استفاده از اتصال گیتهای NAND و NOR در یک ترتیب خاص تولید میشوند تا قادر باشند مدار منطقی ترتیبی مورد نیاز را بسازند.

طبقه بندی مدارهای منطقی ترتیبی

دروازههای منطقی ترتیبی، بلوکهای سازنده مدارات ترکیبی هستند. قفل های دو حالته و فلیپ فلاپها اجزای پایه تشکیل دهنده مدارهای منطقی ترتیبی را میسازند. مدارهای منطقی ترتیبی میتوانند به صورتی ساخته شوند تا مجموعه ای از فلیپ فلاپهای تحریک شونده با گوشه سیگنال کلاک باشند یا ساختار پیچیدهتری همانند ثباتهای ذخیره کننده، دستگاههای حافظه یا شمارندهها داشته باشند. در هر صورت مدارات منطقی ترتیبی می توانند به 3 دستهی زیر طبقهبندی شوند:

حساس به رویداد (Event Driven):

مدارهای غیرسنکرون که وضعیت شان را بلافاصله هنگامی که فعال میشوند، تغییر میدهند.

حساس به کلاک (Clock Driven):

مدارهای سنکرون که به وسیله یک سیگنال کلاک سنکرون شدهاند.

حساس به پالس (Pulse Driven):

که ترکیبی از دو مدار بالا میباشد و به پالسهای محرک پاسخ میدهد.

علاوه بر مدارهای منطقی دو حالتهای که در بالا ذکر شده، مدارهای منطقی وجود دارند که علاوه بر داشتن حالت صفر و حالت یک، دارای المان سومی نیز میباشند که مدارهای منطقی ترتیبی را از مدارهای منطقی ترکیبی جدا میکند و به آنها مدارهای منطقی ترتیبی _ زمان (Time Sequential Logic) اطلاق میشود. این مدارهای هنگامی که ریست میشوند، به وضعیت اولیهشان باز میگردند و مدارهای منطقی ترتیبی با لوپها یا مسیرهای فیدبک مدارهای چرخهای (Cyclic) هستند.

حال می دانیم که در مدارهای ترتیبی، تغییرات تنها زمانی رخ می دهد که اعمال یک پالس کلاک آن را سنکرون کند. در غیر اینصورت مدار غیرسنکرون می باشد و وابسته به ورودی خارجی است. برای حفظ وضعیت فعلی، مدارهای ترتیبی به فیدبک وابسته هستند و بخشی از خروجی با فیدبک به ورودی بازمی گردد. به شکل زیر نگاه کنید.

حلقه فیدبک ترتیبی

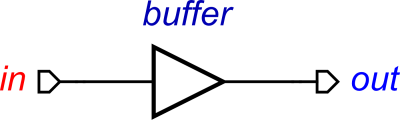

دو گیت منطقی معکوس کننده (دروازههای NOT) به صورت سری به یکدیگر متصل هستند و خروجی در نقطه Q به ورودی فیدبک پیدا میکند. متاسفانه این پیکربندی، هرگز باعث تغییر وضعیت نمیشود چرا که خروجی همواره ثابت خواهد بود. در این مدار، فیدبک نقش اصلی را در تغییر وضعیت به عهده میگیرد. برای درک بهتر طرز کار مدار بهتر است به ساده ترین نوع مدارهای ترتیبی یعنی فلیپ فلاپ SR بپردازیم.

فلیپ فلاپ SR

فلیپفلاپ SR که به قفل SR نیز معروف است، می تواند به عنوان یکی از سادهترین مدارهای تریبی ممکن در نظر گرفته شود. این فلیپ فلاپ ساده یک حافظه دو حالته تک بیتی است که دارای 2 ورودی می باشد که یکی از آنها مدار را “set” میکند؛ به این معنا که وضعیت خروجی یک میشود. و با نماد S مشخص میشود و دیگری مدار را “RESET” می کند. (وضعیت خروجی صفر می شود.) که با نماد R مشخص میشود.

به همین دلیل است که SR مخفف (set-reset) می باشد. ورودی ریست فلیپ فلاپ را به حالت اصلی اش بازمی گرداند و خروجی در نقطه Q یا یک و یا صفر خواهد بود که کاملا بستگی به شرایط SET/RESET دارد. یک گیت NAND در مدار فلیپ فلاپ SR یک فیدبک را از هر دو خروجی به ورودی های مخالف برمی گرداند و به صورت رایج در مدارهای حافظه برای ذخیره یک بیت داده مورد استفاده قرار میگیرد. فلیپ فلاپ SR 3 ورودی دارد: SET، RESET و خروجی Q که بستگی به حالت فعلی یا گذشته دارد.

نام filp flop از طرز کارکرد این مدار گرفته شدهاست. این مدار یا میتواند به حالت منطقی SET، flip کند یا flop back به حالت منطقی RESET داشته باشد.

فلیپ فلاپ SR با گیت NAND

راحتترین راه برای ساختن فلیپ فلاپ SR، اتصال دو جفت گیت NAND به صورتی است که در شکل زیر نشان داده شده. برای تشکیل یک مدار دو حالته Set-Reset که به SR فعال شونده در حالت پایین نیز معروف است، نیاز است تا از هر خروجی به ورودی گیت دیگر فیدبک گرفته شود.

مداری که در شکل بالا نشان داده شده را در نظر بگیرید. اگر ورودی R در سطح منطقی صفر (R=0) باشد و ورودی S در سطح منطقی یک باشد، گیت NAND(Y) حداقل دارای یک ورودی در حالت صفر میباشد. بنابراین خروجی اش در Q به ورودی A فیدبک داده میشود. بنابراین هر دو ورودی گیت NAND (X)، در سطح منطقی “یک” می باشند. پس خروجی این گیت صفر خواهد بود.

بر اساس قاعدهی گیت های NAND اگر ورودی R تغییر وضعیت بدهد و به سطح منطقی “یک” برود و S در سطح منطقی بالا بماند، گیت NAND (Y)، به صورت “R=1” و B=”0” خواهد بود. چرا که یکی از ورودی ها هنوز در سطح منطقی صفر به سر میبرد و خروجی در Q در سطح منطقی یک باقی میماند که به اصطلاح قفل یا set شده روی Q=1 یا Q=0 است.

وضعیت Reset

در دومین وضعیت ثابت، سطح منطقی Q صفر میباشد. در حالیکه خروجی Q’ در سطح منطقی یک است. به عبارتی دیگر R=1 و S=0 خواهد بود.

از آن جایی که یکی از ورودی های دروازه منطقی X صفر می باشد، خروجی Q باید برابر با سطح منطقی یک باشد. سپس از خروجی به ورودی B فیدبک گرفته شود. بنابراین هر دو ورودی گیت های NAND(Y) در منطق یک هستند و Q’ برابر با صفر می شود. اگر ورودی SET (S) تغییر وضعیت بدهد و به منطق یک برود و ورودی R نیز در منطق یک باقی بماند، خروجی Q’ در سطح پایین باقی میماند و هیچ تغییری به وجود نمیآید. بنابراین مدار در حالت “RESET” قفل شده و ما می توانیم SET و RESET را به صورتی که در جدول زیر نشان داده شده تعریف کنیم.

|

وضعیت

|

S

|

R

|

Q

|

--Q

|

توضیحات

|

|---|---|---|---|---|---|

|

Set

|

1

|

0

|

0

|

1

|

Set Q-- >1

|

|

1

|

1

|

0

|

1

|

بدون تغییر

|

|

|

Reset

|

0

|

1

|

1

|

0

|

Reset Q-- > 0

|

|

1

|

1

|

1

|

0

|

بدون تغییر

|

|

|

غیر قابل قبول

|

0

|

0

|

1

|

1

|

شرایط غیر قابل پیشبینی

|

به وضوح میتوان دید هنگامی که هر دو ورودی S=1 و R=1 باشد، خروجی Q و Q’ میتواند یا در سطح منطقی صفر و یا در سطح منطقی یک باشد و خروجی بستگی به حالت قبلی ورودیها دارد. بنابراین شرایط S=R=1 وضعیت خروجیهای Q و Q’ را تغییر نمیدهد.

اما وضعیت S=0 و R=0 یک حالت غیر قابلقبول است و نباید مدار را در این حالت قرار داد چرا که در این حالت هر دو خروجی یک خواهند شد. در حالی که به طور معمولی میخواهیم که Q برعکس Q’ باشد.

در این حالت فلیپ فلاپ کنترل خروجیها را از دست میدهد و اگر دو ورودی پس از این حالت به سطح منطقی یک بروند، فلیپ فلاپ ناپایدار میشود و وضعیت ناپایداری پیدا میکند که در شکل زیر نشان داده شدهاست.

دیاگرام سوییچینگ فلیپ فلاپ SR

این عدم تعادل میتواند باعث شود که یکی از خروجیها سریع تر از دیگری تغییر کند و فلیپفلاپ وارد شرایط غیر قابل پیشبینی شود. به این حالت Meta-Stable میگویند.

بنابراین یک گیت منطقی NAND، فلیپ فلاپ SR یا دروازه NAND SR می تواند توسط اعمال منطق صفر به ورودی SET و توسط اعمال منطق صفر به پایه RESET، ریست شود. اگر هر دو ورودی به صورت همزمان روی منطق یک بروند، شرایط فلیپ فلاپ MetaStable یا ناپایدار خواهد شد.

همان طور که در بالا دیدیم ، فلیپ فلاپ SR که توسط گیت NAND ساخته شده، به منطق صفر در ورودی برای تغییر حالت از Q به Q’ یا برعکس احتیاج دارد. در هر صورت ما می توانیم مدار پایه فلیپ فلاپ را تغییر دهیم تا مداری حاصل شود که با اعمال گوشه بالارونده پالس به ورودیهایش تغییر وضعیت میدهد. در این حالت، باید دو گیت NAND دیگر که با گیت NOT سری شدهاند به فلیپ فلاپ SR متصل شوند. فلیپ فلاپ SR که با گوشهی بالارونده سیگنال ورودی تحریک میشود را در شکل زیر ببینید:

فلیپ فلاپ SR با گیت NAND

علاوه بر استفاده از گیتهای NAND میتوان فلیپ فلاپ های SR تک بیتی را با استفاده از دو گیت NOR که به صورت ضربدری به هم اتصال پیدا کرده اند ساخت. این مدار تا حدی شبیه به مدار بالا میباشد با این تفاوت که ورودیها در حالت بالا فعال میشوند و شرایط غیرقابل قبول در حالتی که ورودی هر دو گیت یک باشد رخ میدهد.

فلیپ فلاپ SR با گیت NOR

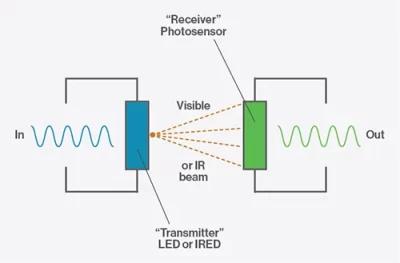

مدار لرزش گیر سوییچ

فلیپ فلاپهای تحریک شونده در گوشههای سیگنال میتوانند پالسهای بدون ریپل تولید کنند. بنابراین یکی از کاربردهای فلیپ فلاپ SR به عنوان (Latch) یا قفل این است که میتواند لرزشهای سوییچ را متوقف کند. همان طور که از نام آن ها پیداست. لرزش سوییچ یا صفحه کلید هنگامی اتفاق میافتد که کانتکتهای مکانیکی سوییچ، کلید فشاری یا صفحه کلید به خوبی روی یکدیگر قرار نمیگیرند و قبل از اینکه سوییچ کاملا بسته شود روی هم میلغزند.

در این شرایط یک سری از پالسها به وجود می آید که ممکن است طول هر کدام به اندازه 10 میلی ثانیه باشد و یک سیستم الکترونیک با کلاک سریع ممکن است این نویز و لرزش ها را به عنوان پالس های منطقی در نظر بگیرد و متعاقبا رفتار دلخواه از خودش نشنا ندهد.

به عنوان مثال، در هنگام لرزش ولتاژ خروجی می تواند به طور شدیدی نوسان کند و چندین پالس ورودی به جای یک پالس دریافت شود. در این حالت از فلیپ فلاپهای SR یا مدارهای قفل دو حالته میتوان برای حذف این مشکل بهره برد. برای درک بهتر به شکل زیر نگاه کنید.

مدار لرزشگیر که با فلیپ فلاپ SR

بسته به حالت حال حاضر خروجی، اگر دکمههای SET یا RESET فشار داده شوند، خروجی به صورتی که در بالا توضیح داده شد تغییر میکند و ورودیهای ناخواسته (که بر اثر لغزش کانتکتها بر روی یکدیگر به وجود آمده) نمیتواند هیچ تاثیری روی خروجی در نقطه ی Q بگذارد.

هنگامی که کلید دوم فشرده میشود، اولین اتصال باعث تغییر وضعیت فلیپ فلاپ میشود و جهشهای سوییچها هیچ تاثیری روی شرایط کلی مدار نخواهد گذاشت. سپس فلیپ فلاپ SR میتواند به صورت اتوماتیک RESET شود.

ICهای رایج و در دسترس طوری ساخته شدهاند که بر مشکل لرزش کانتکتها غلبه کند. از جمله IC های مجهز به لرزش گیر سوییچ می توان به MAX6817، MAX6818 و MAX6816 اشاره کرد. این تراشهها مجهز به یک فلیپ فلاپ داخلی هستند که اجازه نمیدهد لرزشهای سوییچها روی مدارهای دیجیتال تاثیری بگذارد.

قفل های دو حالته SET-RESET می توانند به صورت یک سازنده پالس تک حالته (MonoStable) نیز مورد استفاده قرار بگیرند تا یک پالس تکی در خروجی به وجود بیاید که دارای پهنای باند و بازه زمانی منحصر به فردی است و از آن در فرایندهای کنترلی یا زمانبندی استفاده میشود. قطعه 74LS279 یک قفل SR دو حالته میباشد که شامل 4 گیت NAND دو حالته در یک تراشه است و از آن به عنوان لرزشگیر سوییچ یا کلاک تک حالته یا ناپایدار استفاده میشود.

قفل SR چهارگانه دو حالته 74LS279

فلیپ فلاپ SR دارای گیت یا کلاک

گاهی اوقات در مدارهای منطقی ترتیبی نیاز داریم یک فلیپ فلاپ SR داشته باشیم که تنها زمانی حالتش را عوض میکند که شرایط خاصی فراهم باشد و ارتباطی با تغییر وضعیت SET یا RESET ندارد.

به وسیله اتصال دو گیت AND به صورت سری به رودی های فلیپ فلاپ SR، یک فلیپ فلاپ دارای دروازه ساخته میشود. ورودی های گیت AND فعال ساز هستند و پیشوند EN دارند. اضافه کردن این ورودی به این معناست که خروجی در نقطه Q تنها زمانی وضعیتش را تغییر می دهد که در سطح بالا باشد و بنابراین می تواند به عنوان یک ورودی CLK به کار رود. برای درک بهتر به شکل زیر نگاه کنید.

هنگامی که ورودی فعال ساز (EN) در سطح منطقی صفر می باشد، خروجی های دو گیت AND نیز در سطح صفر می باشد و فارغ از اینکه شرایط دو ورودی R و S به چه صورتی است، خروجی Q و Q’ روی حالت قبلی خود قفل میشوند.

هنگامی که ورودی EN به سطح یک منطقی میرود، مدار همانند یک فلیپ فلاپ SR دو حالته عمل میکند.

همچنین ورودیهای فعالساز میتواند به یک سیگنال کلاک متصل شوند تا از طریق سیگنال کلاک سنکرون شوند که این نوع فلیپ فلاپها به فلیپ فلاپهای SR دارای کلاک معروفاند.

بنابراین یک فلیپ فلاپ دو حالته SR دارای دروازه، همانند یک قفل دو حالته معمولی عمل میکند با این تفاوت که خروجی زمانی فعال میشود که منطق یک به ورودیهای فعال ساز اعمال شده و با منطق صفر غیرفعال می شود.

در مقالهی بعدی به نوع دیگری از فلیپ فلاپها می پردازیم که طرز کارشان به فلیپ فلاپ های SR شباهت دارد و فلیپ فلاپ JK نامیده میشود چرا که سازنده آن Jack Kilby بوده. این فلیپ فلاپ ها پر کاربردترین نوع فلیپ فلاپ هستند. بنابراین یک المان همگانی محسوب میشود.