منبع جریان ثابتFET از JFET ها و MOSFET ها برای ارائه جریان باری استفاده میکنند که علیرغم تغییر در مقاومت بار یا ولتاژ تغذیه ثابت میماند.

منبع جریان ثابت FET نوعی مدار فعال است که از ترانزیستور اثر میدانی برای تامین جریان ثابت مدار استفاده میکند. اما شاید از خودتان بپرسید برای چه به جریان ثابت نیاز داریم؟ منابع جریان ثابت و سینکهای جریان، (سینک جریان معکوس منبع جریان است) روشی بسیار ساده برای تشکیل مدارهای بایاس یا ایجاد ولتاژ مرجع با مقدار جریان ثابت هستند.

منابع جریان ثابت معمولاً در مدارهای شارژ خازن به منظور دستیابی به اهداف زمانبندی دقیق یا در برنامههای شارژ باتری قابل شارژ، و همچنین مدارهای LED خطی برای تولید روشنایی ثابت استفاده میشوند.

مدارات ولتاژ مرجع مقاومتی بر اساس منابع ثابت جریان پایهگذاری میشوند، چرا که اگر شما مقدار مقاومت و جریانی که از آن میگذرد را بدانید با استفاده از قانون اهم میزان افت ولتاژ به دست میآید و اگر جریان و مقاومت ثابت باشند، افت ولتاژ نیز ثابت خواهد بود اما برای ساخت یک منبع جریان ثابت بدون نقص باید به برخی از ویژگیهای FET و محاسبه دقیق مقدار مقاومت توجه کرد تا جریان تبدیل به ولتاژی دقیق و ثابت شود.

ترانزیستورهای اثر میدانی معمولاً برای ایجاد منبع جریان با Junction-FET (JFET) استفاده میشوند و MOSFET نیمههادی اکسید فلز در حال حاضر در برنامههای کاربردی با منبع جریان پایین استفاده میشود.

در ساده ترین شکل خود، JFET می تواند به عنوان یک مقاومت کنترل شده با ولتاژ استفاده شود که با اعمال یک ولتاژ کوچک در گیت میزان هدایت کانال قابل کنترل خواهد بود .

ما در بخش مربوط به JFETها خواندیم که ترانزیستورهای اثر میدان پیوندی تنها در مد تخلیه عمل میکنند و یک JFET کانال N به صورت پیشفرض روشن میباشد اما اگر ولتاژ گیت ــ سورس (VGS) به حد کافی منفی شود، ترانزیستور خاموش میشود JFET کانال P نیز به صورت پیشفرض روشن میباشد و اگر ولتاژ گیت ــ سورس به اندازه کافی مثبت شود میتواند آن را خاموش کند.

بایاس JFET کانال N

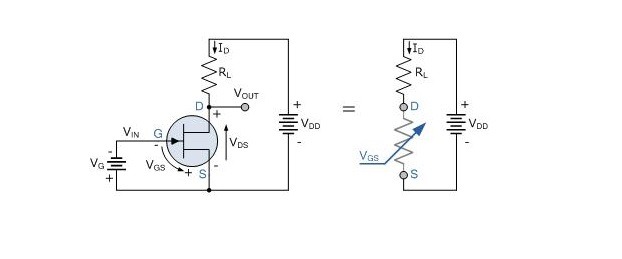

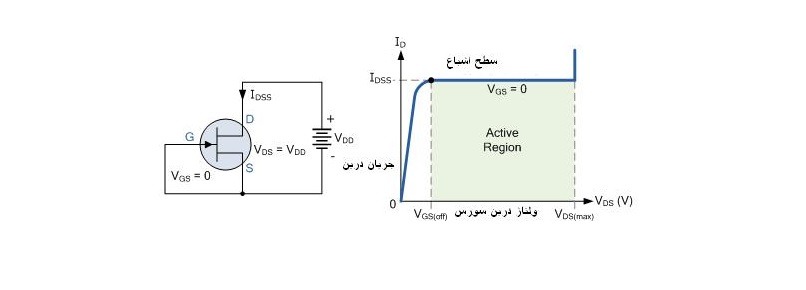

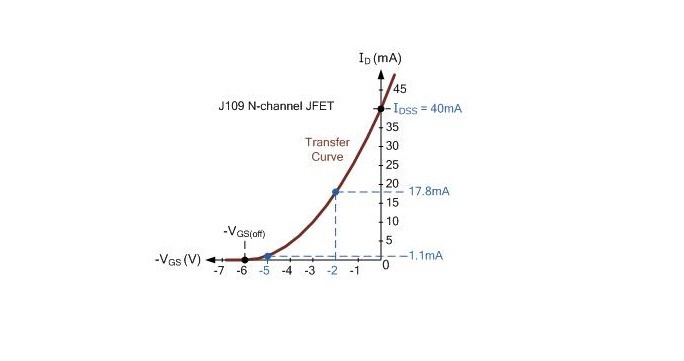

در تصویر اتصالات استاندارد یک مدار سورس مشترک کانال N که در آن JFET در ناحیه فعال قرار گرفته مشاهده میشود. ولتاژ گیت ــ سورس (VGS) برابر با تغذیه گیت میباشد، پیوند گیت ــ منبع به صورت معکوس بایاس شده و VDD ولتاژ درین به منبع (drain-to-source) را تأمین میکند. ID معرف جریانی است که از منبع به درین در حال عبور است.

ولتاژ درین ــ سورس (VDS) افت ولتاژ بایاس مستقیم JFET است و به صورت تابعی از جریان درین تعریف میشود. هنگامی که VDS به مینیمم مقدار خود میرسد کانال هدایت JFET کاملاً باز میشود و IDبه ماکزیمم مقدار خود میرسد که ID(SAT) یا جریان اشباع درین به سورس نامیده میشود.

هنگامی که VDS در ماکزیمم مقدار خود قرار دارد، کانال هدایت JFET کاملاً بسته است بنابراین ID به صفر تنزل پیدا میکند و ولتاژ درین ــ سورس (VDS) مساوی با ولتاژ تغدیه درین (VDD) میشود. در این حالت ولتاژ گیت (VGS) که با رسیدن به آن هدایت کانال JFET متوقف میشود ، ولتاژ قطع گیت (VGS(OFF)) نامیده خواهد شد.

پیکربندی سورس مشترک کانال N عملکرد ثابت JFET را در صورت عدم وجود سیگنال ورودی تضمین میکند VIN همانند VGSو ID متغیرهای حالت ثابت میباشد.

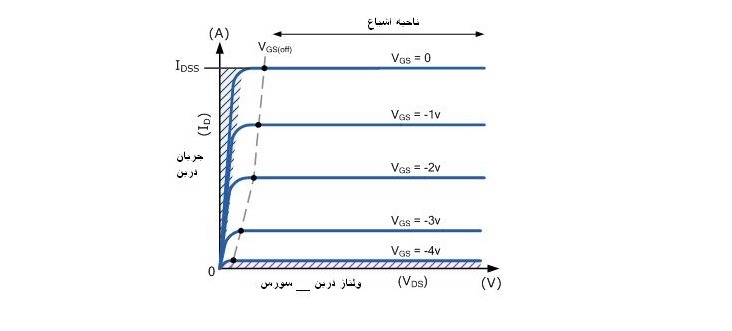

بنابراین برای یک JFET سورس مشترک، ولتاژ گیت ــ سورس (VGS) میزان جریانی که از کانال هدایتی بین درین و سورس میگذرد را کنترل میکند و بنابراین منحنی مشخصه خروجی بر اساس تغییرات ID نسبت به VGSقابل رسم میباشد.

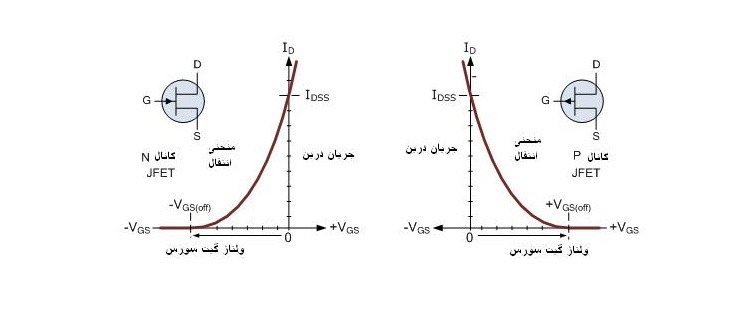

منحنی مشخصه خروجی JFET کانال N

JFET به منزله منبع ثابت جریان

طبق تعاریف بالا متوجه شدیم که JFET در حالت پیشفرض روشن میباشد و اگر VGS به اندازه کافی منفی باشد، کانال هدایتی درین ــ سورس بسته خواهد شد. در این حالت ترانزیستور به ناحیه قطع میرود و جریان درین برابر با صفر میشود در یک JFET کانال N، بسته شدن کانال هدایتی بین درین و سورس بر اثر عریض شدن ناحیه تخلیه نوع P که اطراف گیت وجود دارد، رخ میدهد. در JFET کانال P ناحیه تخلیه از نوع N است.

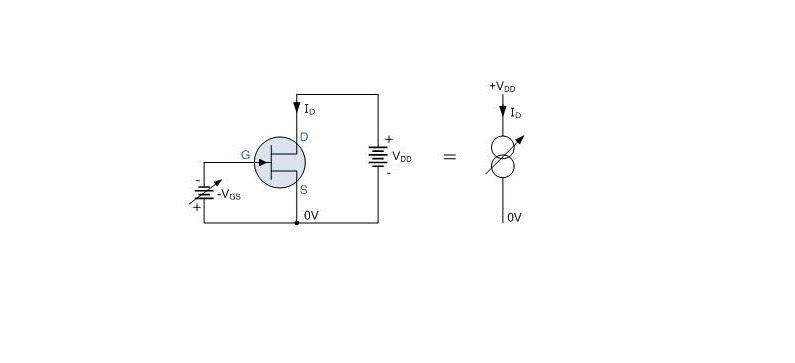

بنابراین با اعمال ولتاژ گیت ــ سورس معین، جریانی بین صفر تا IDSS از کانال هدایت عبور میکند مدار زیر را در نظر بگیرید.

بایاس JFET با ولتاژ صفر

متوجه شدیم که منحنی مشخصه خروجی JFET تغییرات ID نسبت به تغییرات VGS را در حالتی که VDS ثابت است نشان میدهد. همچنین دریافتیم که منحنیهای JFET حتی با اعمال تغییرات فوقالعاده شدید در VDS تغییر چندانی نخواهد کرد بنابراین VDS برای تعیین یک نقطه راهاندازی ثابت در کانال هدایتی بسیار مناسب خواهد بود.

سادهترین منبع جریان ثابت با اتصال کوتاه کردن گیت JFET با ترمینال سورس به دست میآید. در این حالت کانال هدایتی JFET کاملاً باز میشود و جریانی که از آن عبور میکند به ماکزیمم مقدار خود میرسد. در چنین شرایطی JFET به حالت اشباع میرود با وجود این راهاندازی و کارکرد چنین مدار جریانی چندان راضیکننده نیست چرا که مقدار IDSS کاملاً وابسته به نوع المانهای به کار رفته در پیکربندی است.

به عنوان مثال 2N36XX یا 2N43XX از سری کانال N، ترانزیستورهای پیوندی اثر میدانی هستندکه تنها میتوانند جریانهای پایین را از خود عبور دهند، اما سری کانال N ، J1XX یا PN4XX قابلیت تحمل جریانهای بالا را دارند. همچنین فراموش نکنید که IDSS حتی بین ترانزیستورهای مختلف از یک سری تفاوت دارد و برای پیدا کردن مشخصات ترانزیستورهای مختلف حتماً باید به دیتاشیت آن که توسط کارخانه سازنده ارائه شده رجوع کرد.

نکته دیگر این است که JFETها در اصل مقاومتهایی هستند که با ولتاژ کنترل میشوند و کانال هدایتی شان به صورت مقاومت متغیری عمل میکند، که با ترمینال درین و سورس سری شده است. مقاومت کانال هدایتی RDS نامیده میشود. همانطور که در گذشته به آن اشاره شد، هنگامی که VGS=0 بیشترین جریان از درین به سورس عبور میکند، مقدار RDS به پایینترین حد میرسد.

مقاومت کانال هرگز کاملاً صفر نمیشود، مینیمم مقاومت کانال FET معمولاً در دیتاشیت قطعه ذکر شده و حتی ممکن است تا ۵۰ اهم نیز بالا برود. هنگامی که FET در حال هدایت جریان میباشد مقاومت کانال RDS(ON) نام میگیرد و اگر VGS=0 این مقاومت به کمترین مقدار خود میرسد. در ضمن مقادیر بالای RDS میزان هدایت کانال را کاهش میدهد.

بنابراین JFET میتواند به گونهای بایاس شود که به عنوان یک منبع ثابت جریان عمل کند هنگامی که JFET در ناحیه قطع قرار میگیرد، جریان درین صفر و کانال به طور کامل بسته میشود. بنابراین به منظور اینکه یک جریان ثابت از ترانزیستور عبور کند، باید JFET را به ناحیه فعال ببریم.

منحنی انتقال JFET

فراموش نکنید که برای یک JFET کانال P، ولتاژ گیت در ناحیه قطع، ولتاژی مثبت میباشد اما جریان اشباع در حالتی قابل دستیابی است که VGS به صفر ولت برسد که این شرط بین JFET کانال P و کانال N مشترک میباشد. همچنین منحنی انتقال غیرخطی میباشد چرا که افزایش جریان درین در حالتی که VGS به صفر نزدیک میشود سیر تصاعدی دارد.

بایاس JFET با ولتاژ منفی

به یاد داریم کهJFET همواره در مد تخلیه و پیشفرض روشن قرار دارد. بنابراین به یک ولتاژ گیت منفی در نوع کانال N و ولتاژ گیت مثبت در نوع کانال P برای خاموش کردن ترانزیستور نیاز است بایاس کردن یک JFET کانال N با ولتاژ مثبت یا بایاس JFET کانال P با ولتاژ منفی، کانال هدایتی را عریضتر میکند و جریان حتی از مرز اشباع نیز میگذرد.

با نگاه به منحنی مشخصه میتوانیم با انتخاب ولتاژ گیت درست، جریانی ثابت را از ترانزیستور دریافت کنیم.

اما اگر بخواهیم مدار جریان دقیقتری داشته باشیم، بهتر است که JFET را با ۱۰ الی ۵۰ درصد جریان ناحیه اشباع بایاس کنیم. در این حالت افت توان در کانال فوقالعاده کم میشود و درنتیجه افزایش دمای ترانزیستور به حداقل میرسد.

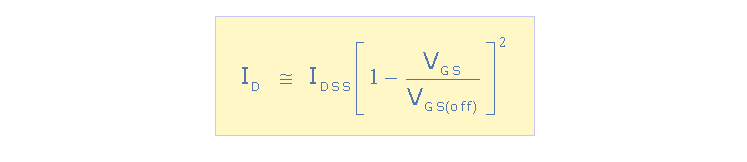

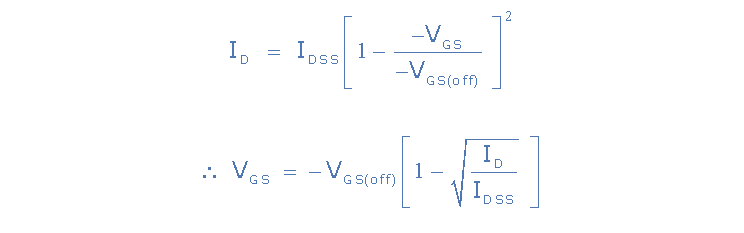

برای مقادیر مختلف VGS ، جریان ID به صورت زیر قابل محاسبه خواهد بود:

معادله جریان JFET

مثال شماره (۱)

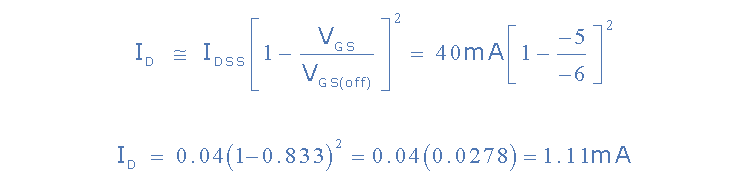

یک ترانزیستور اثر میدان از نوع J109 کانال N دارای جریان اشباع (IDSS) ۴۰ میلی آمپر میباشد و ماکزیمم مقدار VGS در حالت قطع ۰/۶ است حال با در نظر گرفتن این مقادیر میزان جریان درین را برای VGS=0 ، VGS=-2،VGS=-5 محاسبه کنید. همچنین منحنی انتقال J109 را به دست بیاورید.

1- هنگامی که VGS=0v باشد.

هنگامی که VGS=0v است کانال هدایتی ترانزیستور باز میباشد و حداکثر جریان از درین عبور میکند بنابراین: ID=IDSS=40mA

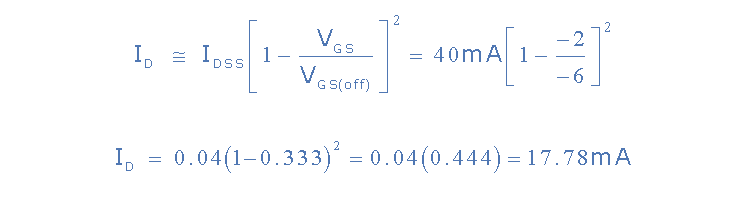

۲) هنگامی که VGS=-2v

3) هنگامی که VGS=-5v

۴) منحنی انتقال J109

بنابراین خواهیم دید هنگامی که ولتاژ گیت ــ سورس (VGS) به ولتاژ گیت ــ سورس در ناحیه قطع نزدیک میشود، جریان درین کاهش مییابد. در این مثال، جریان درین در دو نقطه محاسبه شده اما استفاده از مقادیر بیشتر VGS بین صفر ولت تا ناحیه قطع، شکل دقیقتری از منحنی را در اختیار ما قرار میدهد.

منبع جریان JFET

یک ترانزیستور JFET میتواند به گونهای ساخته شود که به ازای ولتاژ معینی، جریان ثابتی را از خود عبور دهد. برای نیل به این منظور نیاز به اعمال VGS– در ترانزیستور کانال N و اعمال VGS+ در ترانزیستور کانال P خواهیم داشت، اما مشکل اینجاست که در این حالت JFET به دو نوع منبع تغذیه مجزا نیاز دارد (یکی برای VDD و دیگری برای VGS)

به هر حال اگر یک مقاومت را بین سورس و زمین قرار دهیم، میتوانیم به یک ترکیب خودبایاس VGS برای JFET دست یابیم تا به این وسیله به عنوان یک منبع ثابت جریان معرفی شود، در این حالت مدار تنها به ولتاژ تغذیه VDD نیاز دارد.

درنگاه اول، اینطور به نظر میرسد که این پیکربندی شبیه به پیکربندی درین مشترک میباشد اما در این مدار ترمینال گیت مستقیماً به زمین متصل شده (VG=0) ولتاژ سورس به دلیل افت ولتاژ در طول مقاومت سورس بالاتر از صفر میباشد بنابراین یک کانال جریان به وجود خواهد آمد که از مقاومت خارجی که به سورس متصل شده میگذرد و و لتاژ گیت ــ سورس JFET کمتر از صفر خواهد شد. (VGS<0)

مقاومت خارجی سورس (RS) ولتاژ فیدبکی را به وجود میآورد که با بایاس کردن ترمینال گیت جریان درین را با وجود تغییرات در ولتاژ درین ــ سورس ثابت نگه میدارد بنابراین تنها منبع تغذیهای که به آن نیاز داریم، VDD است که تامینکننده جریان درین و بایاس خواهد بود. بنابراین JFETها از افت ولتاژ در طول مقاومت سورس برای تنظیم ولتاژ بایاس گیت و جریان کانال استفاده میکنند و افزایش مقدار RS میزان جریان درین ID راکاهش خواهد داد، اما اگر قصد داشته باشیم مدار ثابت جریان تولید کنیم، باید مقدار مناسبی را برای مقاومت خارجی سورس انتخاب کنیم.

دیتاشیت کارخانه سازنده برای JFET کانال N مقدار VGS(OFF)و IDSS را در اختیار ما قرار میدهد که با دانستن مقدار این دو پارامتر و داشتن معادله JFET میتوانیم ولتاژ گیت ــ سورس را به ازای هر ID به دست بیاوریم همانطور که گفته شد، ID بین صفر تا IDSS متغیر است.

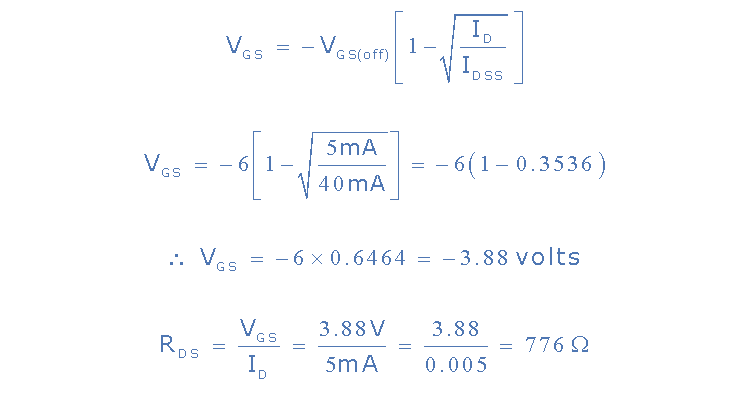

معادله ولتاژ گیت ــ سورس در JFET

با داشتن ولتاژ گیت ــ سورس و جریان درین ، مقاومت بایاس سورس RS به راحتی از طریق قانون اهم (R=V/I) قابل محاسبه خواهد بود.

معادله مقاومت سورس JFET

مثال شماره (۲)

در این مثال دوباره از J109 کانال N استفاده شده که در شرایطVGS=0 ، IDSS=4mA قرار دارد و ماکزیمم مقدار VGS(OFF)=0.6 میباشد با استفاده از دادههای بالا مقدار مقاومت خارجی سورس را برای ساختن یک کانال ثابت جریان ۲۰ میلی آمپری و ۵ میلی آمپری محاسبه کنید.

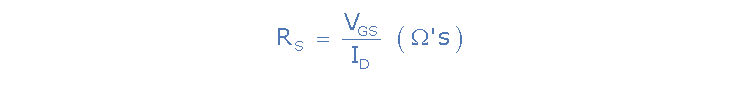

۱) VGS برای ID=20mA

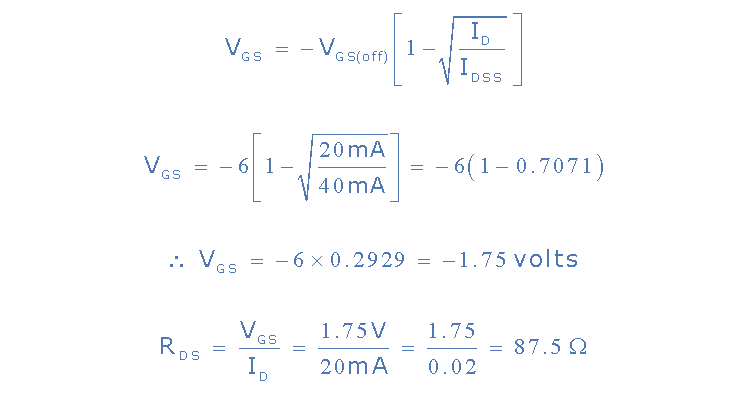

۲) VGS برای ID=5mA

بنابراین با داشتن VGS(OFF)و IDSS و با استفاده از معادلات بالا میتوان مقاومت سورس مورد نیاز را برای بایاس گیت به منظور رسیدن به جریان درین دلخواه محاسبه کرد که در این مثال به ازای ۲۰ میلی آمپر، مقاومت سورس برابر با ۸۷/۵Ω و برای ۵ میلی آمپر، مقاومت سورس ۷۷۶Ω میباشد. بنابراین با اضافه کردن یک مقاومت خارجی در سورس میتوانیم جریان خروجی سورس را کنترل کنیم.

اگر مقاومتهای ثابت سورس با پتانسیومتر (Potentiometer) جایگزین شوند، میتوان یک منبع جریان ثابت قابل تنظیم را به وجود آورد. به عنوان مثال دو مقاومت بالا با یک پتانسیومتر جایگزین میشود که علاوه بر قابل تنظیم بودن، جریان درین حتی با ایجاد تغییرات در VDS ثابت باقی خواهد ماند.

مثال شماره (۳)

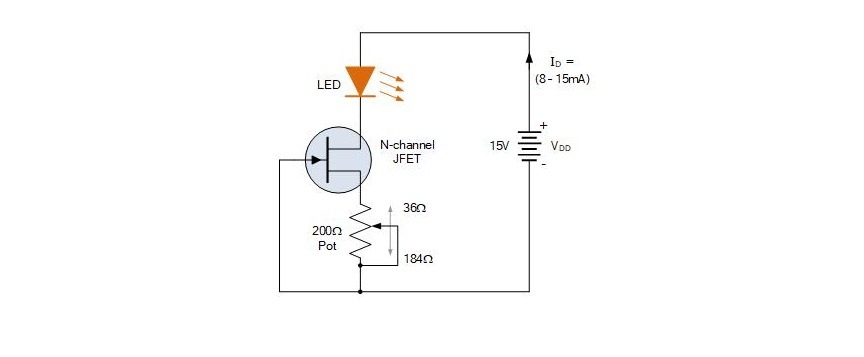

یک JFET کانال N برای تغییر میزان روشنایی یک LED نیاز است. جریانی که به LED اعمال میشود میتواند بین ۸ تا ۱۵ میلی امپر تغییر کند اگر منبع جریان ثابت JFET از یک منبع تغذیه DC (۱۵ ولت) استفاده کند، مقدار مقاومت سورس را برای حداقل و حداکثر روشنایی LED در حالتی که VGS(OFF)=-0/4 و IDSS=20mA است را محاسبه و دیاگرام مدار را رسم کنید.

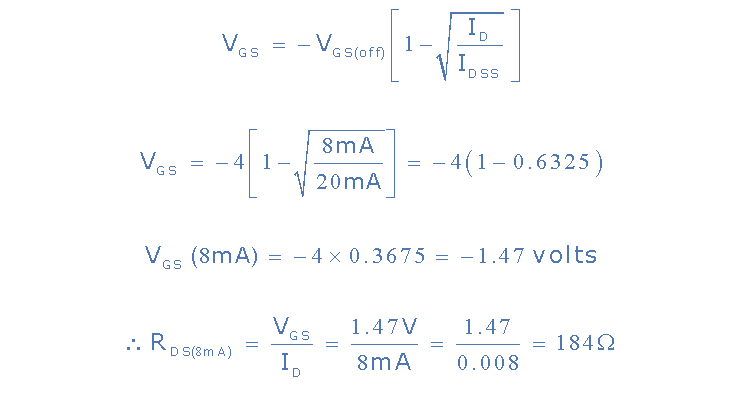

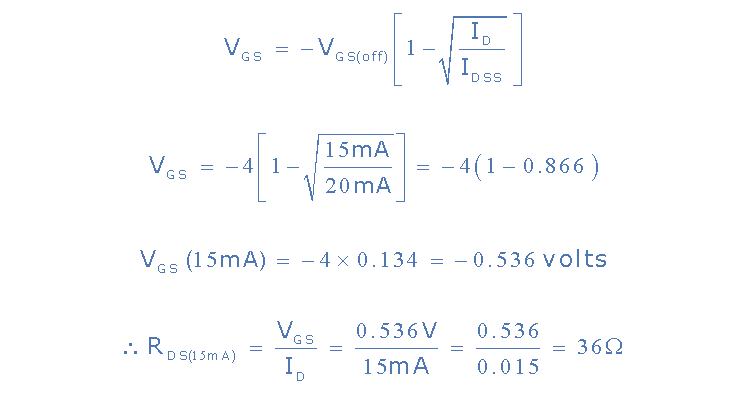

۱) VGS برای جریان درین ۸ میلی آمپری

۲) VGS برای جریان درین ۱۵ میلی آمپری

در این شرایط ما به یک پتانسیومتر خارجی که میتواند مقاومتش را بین ۳۶Ω تا ۱۸۴Ω تغییر دهد نیاز خواهیم داشت. در نتیجه مناسبترین پتانسیومتر برای ما پتانسیومتر ۲۰۰Ω خواهد بود.

منبع جریان ثابت قابل تنظیم JFET

با متغیر بودن RS جریانی که از کانال هدایت میگذرد نیز قابل تنظیم و تغییر خواهد بود حال به منظور پایدارسازی جریان کانال بهتر است که ماکزیمم جریانی که از LED میگذرد را محدود کنیم. در مثال بالا این مقدار ۱۵ میلی آمپر در نظر گرفته شده است.

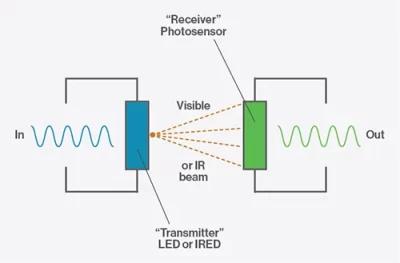

ساختن منبع جریان به وسیله ماسفتها، قابلیت تنظیم بهتر جریان و بالا بردن مقدار منبع جریان را برای ما فراهم میآورد. ماسفتها بر خلاف JFET ها دارای دو مد افزایشی و تخلیه هستند، بنابراین میتوان انواع متنوعتری از منابع جریان را به وسیله آنها ایجاد کرد.

خلاصه

همانطور که دیدید، ترانزیستورهای اثر میدان به دلیل مشخصات مقاومت کانالشان میتوانند تبدیل به منابع ثابت جریان شوند. این منابع در مواقعی استفاده میشوند که قرار باشد باری را با جریان ثابت تغذیه کنیم.

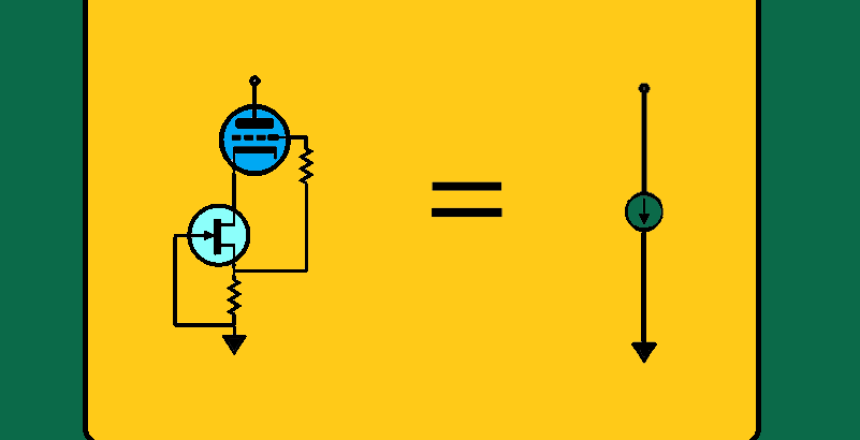

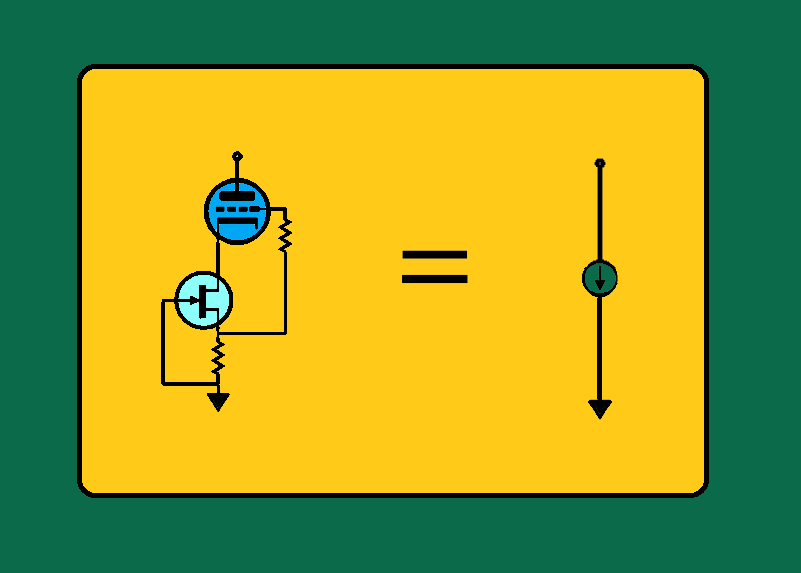

گفتنی است منابع ثابت جریان توسط ترانزیستورهای پیوندی دو قطبی نیز قابل راه اندازی هستند حتی میتوان از ترکیب ترانزیستورهای FET و BJT برای ساخت این نوع منابع بهره برد.

فراموش نکنید که JFET بر خلاف BJT المانی است که با ولتاژ کنترل میشود.

یکی از مهمترین خصیصههای JFET این است که در مد تخلیه کار میکند، بنابراین کانال هدایتی به طور پیشفرض باز است و تنها با اعمال ولتاژ گیت ــ سورس مناسب بسته خواهدشد.

VGS از صفر ولت ( ماکزیمم هدایت کانال) تا چندین ولت منفی برای خاموش شدن کامل المان تغییر میکند، بنابراین با بایاس کردن ترمینال گیت در بین مقادیر VGS(OFF) و صفر میتوانیم عرض ناحیه تخلیه کانال و متعاقباً میزان مقاومت آن را کنترل کنیم.

تنظیم و تلورانس منابع ثابت جریان JFET بستگی به مقدار جریان درین دارد. هر چقدر جریان درین پایینتر باشد قابلیت تنظیم المان بیشتر خواهد شد. بایاس JFET با جریان درینی بین ۱۰ تا ۵۰ درصد جریان ناحیه اشباع کارایی ترانزیستور رابه حداکثر خواهد رساند که برای نیل به این منظور از یک مقاومت خارجی که بین ترمینال گیت و سورس نصب شده استفاده میشود.

مقاومت فیدبک گیت ــ سورس در منابع ثابت جریان، مقاومت خود بایاس نیز نامیده میشوند و ترانزیستور را قادر میکند به عنوان یک منبع ثابت جریان در هر جریانی زیر IDSS راهاندازی شود. این مقاومت خارجی میتواند ثابت یا با استفاده از پتانسیومتر قابلتغییر باشد.