فهرست مطالب

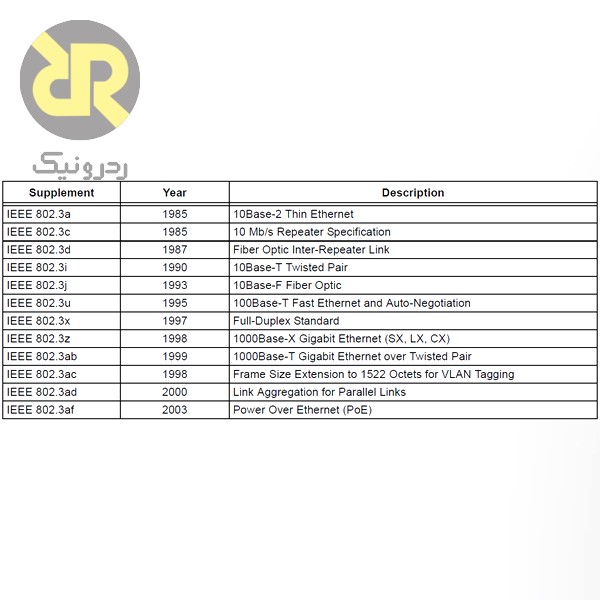

Ethernet یک پروتکل دسترسی چندگانه با قابلیت شنود سیگنال حامل[1] آسنکرون با طول Payload بین 46 تا 1500 بایت و نرخ داده صدها مگابایت در ثانیه است. این پروتکل، یک پروتکل لایه data link و Physical است که استاندارد IEEE 802.3 مشخصههای آن را مشخص کرده است. مشخصههای Ethernet در سالیان اخیر برای داشتن سرعت انتقال بالاتر و ارایه قابلیتهای جدید گسترش یافته است. در جدول 1 برخی از استانداردهای رایج Etrhernet نشان داده شده است. لازم به ذکر است که Ethernet در کاربردهای Low power ، گزینه مناسبی نیست.

ساختار فریم Ethernet

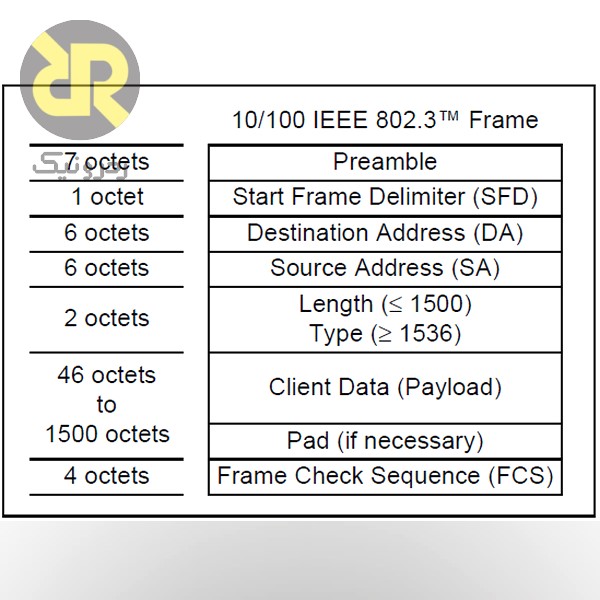

ساختار فریم بیسیک10/100 Ethernet در شکل 5 نشان داده شده است.

Preamble: این فیلد برای بازیابی داده و کلاک در نظر گرفته شده است که شامل 7 بایت متوالی 0x55 است.

Start-of-Frame Delimiter: این فیلد که گاهی اوقات بخشی از Preamble در نظر گرفته میشود بصورت 0b10101011 است.

(Destination Address (DA: آدرس MAC مقصد است که طول آن 6 بایت است.

(Source Address (SA: آدرس MAC مبدا است.

Length/Type: در صورتی که مقدار این فیلد کمتر از 1500 باشد، طول Payload را مشخص میکند. در غیر اینصورت نوع Payload را تعیین میکند. متداول ترین انواع Payload عبارتند از:

IPv4 = 0x0800

IPv6 = 0x86DD

ARP = 0x0806

RARP = 0x8035

Payload: داده موردنظر در این فیلد قرار میگیرد. حداقل طول Payload، 46 بایت و حداکثر طول آن 1500 بایت است.

Pad: در صورتیکه طول Paylaod کمتر از 46 بایت باشد، تعدادی بایت در فیلد Pad به فریم اضافه میشود تا محدودیت حداقل طول فریم را رعایت کند.

(Frame Check Sequence (FCS: چهار بایت CRC فریم است که برای تشخیص خطای احتمالی قرار داده شده است.

(End-of-Stream Delimiter (ESD: در اترنت 100 Mbit/s این فیلد انتهای فریم را مشخص میکند.

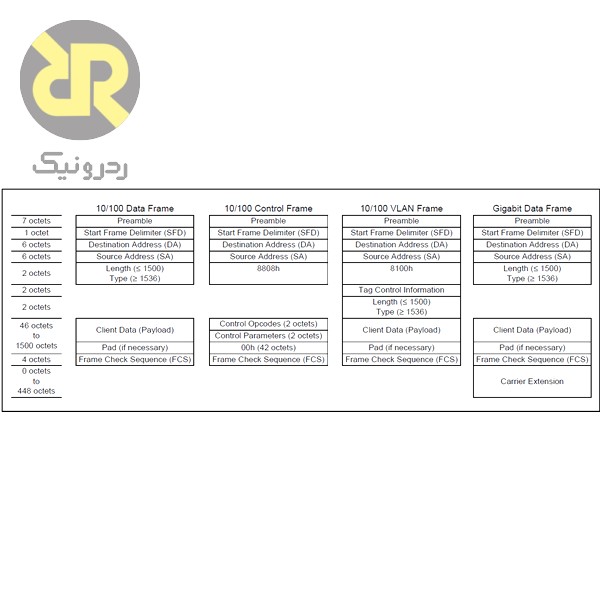

همانطورکه در قسمتهای بیان شد، مشخصههای Ethernet سالیان اخیر بسیار گسترش یافته است. در شکل ** ساختار فریم استانداردهای رایج Ethernet نشان داده شده است.

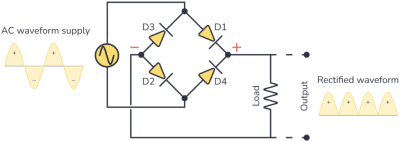

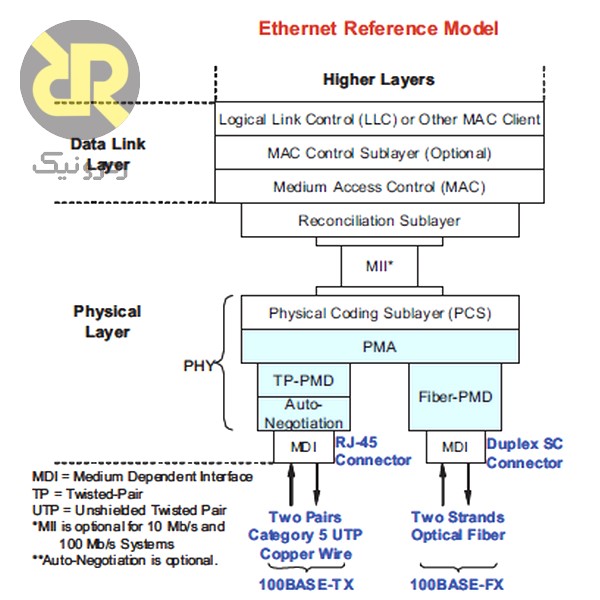

زیرلایه های MAC و PHY

در بخشهای اول این گزارش در مورد جایگاه پروتکل Ethernet در لایههای پیوند داده و فیزیکی در مدل TCP/IPتوضیح داده شد. در Ethernet اصطلاحاً به لایه پیوند داده، لایه MAC گفته میشود. از استاندارد Ethernet سریع به بعد، برای تشریح بهتر چگونگی عملکرد اترنت و پیاده سازی عملی آن، عملکرد اترنت در این دو لایه به زیر لایههای مختلف تقسیم بندی شد. در این بخش در مورد هر یک از زیر لایه های MAC و PHY صحبت خواهد شد. لایههای MAC و PHY در استاندارد IEEE 802.3 و سرعت 100 Mb/s در شکل 7 نشان داده شده است.

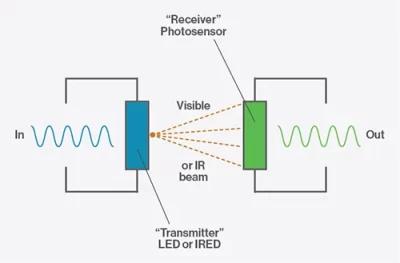

واسط فیزیکی برای اتصال به رسانه انتقال MDI (Media Dependent Interface) نامیده میشود و با توجه به نوع رسانای مورد استفاده (کابل CAT، فیبر نوری و …) تغییر میکند.

واسط بین لایه MAC و PHY را MII (Media Independent Inteface) مینامند و دارای یک مسیر فرستنده و یک مسیر گیرنده و یک مسیر برای مدیریت است که برای خواندن و نوشتن در رجیسترهای PHY استفاده میشود. عرض مسیر فرستنده و گیرنده یکسان است و با توجه به سرعتی که لایههای MAC و PHY پیاده سازی میکنند متفاوت است مانند:

- 10 Mbit/s: که عرض 2 بیت در فرکانس 5 MHz

- 100 Mbit/s: که عرض 4 بیت در فرکانس 25 MHz

Reconciliation Layer

کد کردن، مالتی پلکس کردن و همزمانسازی جریان سمبلهای خروجی بر عهده این بخش است.

Physical Medium Attachment

انجام اعمالی مانند Serialization، Deserialization، بازیابی کلاک و … بر روی جریان سمبلهای ورودی و خروجی بر عهده این بخش میباشد.

Auto-Negotiation

تنظیم مشخصات ارتباط بر عهده این بخش است.

Medium Dependent Interface/Physical Media Dependent MDI/PMD

شامل تراشه transceiver برای پیادهسازی ارتباط در شبکه و کانکتور RJ-45 است.

Medium

مانند کابلهای UTP ، فیبر نوری و…

طرح اصلی MII برای کاهش تعداد سیگنالها و افزایش سرعت گسترش یافته است که در زیر انواع آن آورده شده است:

v reduced media-independent interface RMII

Ø The two clocks TXCLK and RXCLK are replaced by a single clock. This clock is an input to the PHY rather than an output, which allows the clock signal to be shared among all PHYs in a multiport device, such as a switch.

Ø The clock frequency is doubled from 25 MHz to 50 MHz, while the data paths are narrowed to 2 bits rather than 4 bits.

Ø RXDV and CRS signals are multiplexed to one signal.

Ø The COL signal is removed.

v gigabit media-independent interface GMII

Ø speeds up to 1000 Mbit/s

Ø data interface clocked at 125 MHz

Ø eight-bit data paths for receive and transmit

Ø can also operate on fall-back speeds of 10 or 100 Mbit/s

v reduced gigabit media-independent interface RGMII

Ø uses half the number of data pins as used in the GMII interface

Ø clocking data on both the rising and falling edges of the clock in 1000 Mbit/s

Ø eliminating non-essential signals (carrier-sense and collision-indication

v serial gigabit media-independent interface SGMII

Ø uses differential pairs at 625 MHz clock frequency for TX and RX data and TX and RX clocks

Ø Transmit and receive path each use one differential pair for data and another differential pair for clock

Ø low-power and low pin-count serial 8b/10b-coded interface

v Quad serial gigabit media-independent interface QSGMII

Ø combining four SGMII lines into a 5 Gbit/s interface

v 10 gigabit media-independent interface

Ø a standard defined in IEEE 802.3 for connecting full duplex 10 Gigabit Ethernet

Ø It is composed from two 32-bit datapaths (Rx & Tx) and two four-bit control flows (Rxc

and Txc, operating at 156.25 MHz DDR 312.5 MT/s

بلوک دیاگرام اتصال به شبکه اترنت

به طور کلی با توجه به تراشههای مورد استفاده در طراحی، چهار حالت برای اتصال به شبکه اترنت در کاربردهای embedded وجود دارد:

حالت اول:

در این حالت لایههای فیزیکی و پیوند داده (شامل دو زیر لایه MAC و LLC) در میکروکنترلر وجود دارد و نیازی به استفاده از تراشههای جانبی وجود ندارد.

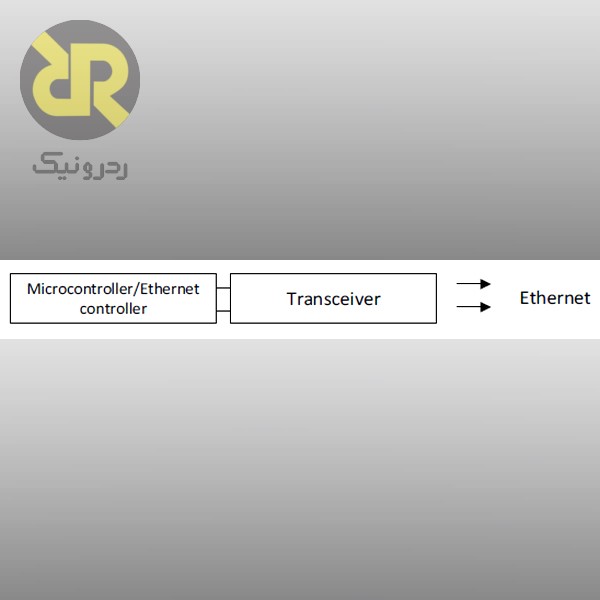

حالت دوم:

در این حالت لایه پیوند داده در میکروکنترلر و لایه فیزیکی توسط تراشه Transceiver پیاده سازی میشود، البته معمولاً حالت اول متداولتر است و میکروکنترلرهایی که دارای اترنت هستند، لایه فیزیکی را نیز پیاده سازی میکنند.

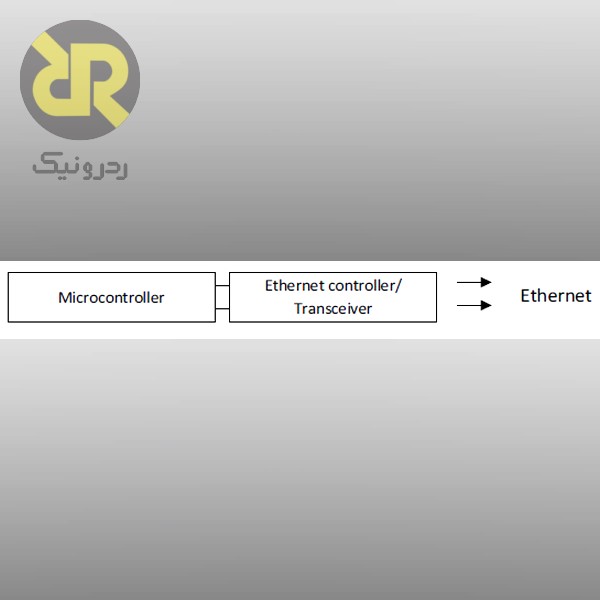

حالت سوم:

در این حالت لایه پیوند داده و لایه فیزیکی توسط تراشه Ethenet Controller پیاده سازی میشود.

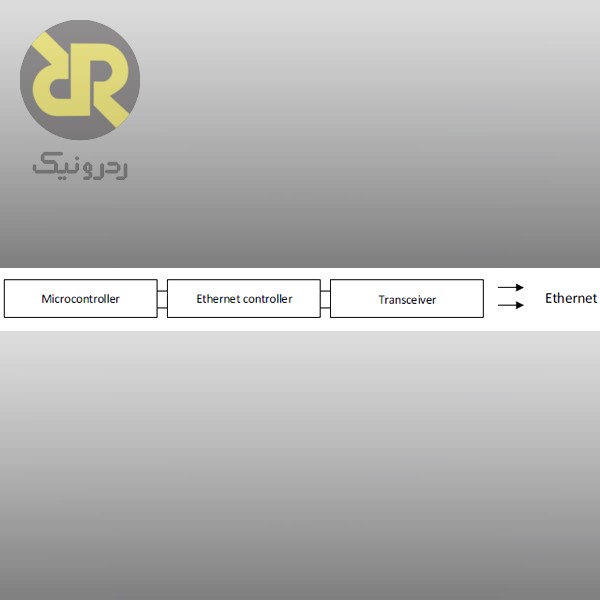

حالت چهارم:

در این حالت لایه پیوند داده در تراشه Ethernet Controller و لایه فیزیکی در تراشه Tranciever پیاده سازی میشود.

معرفی تراشه های Tranciver

در این بخش برخی از آیسیهای tranciver های قابل موجود در بازار بررسی شده اند.

- RTL8201

- سازگاری با استاندارد MIIبرای ارتباط با تراشه لایه پیوند داده

- پشتیبانی از سرعتهای 100Mbit/s و 10Mbit/s

- دارای پکیج 48 پایه LQFP

- DM916

- مطابق استانداردهای 10Base-T و BASE-TX

- طبق استاندارد 3u برای 100BASE-TX شامل تمام استانداردهای لایه فیزیکی

- پشتیبانی از auto-negotiation برای تشخیص نوع و سرعت ارتباط

- شامل فیلترهای جانبی، بدون نیاز به فیلترهای خارجی برای اتصال به شبکه

- سازگاری با استاندارد MII برای ارتباط با تراشه لایه پیوند داده

- DP83848

- پشتیبانی از سرعتهای 10Mbit/s و 100Mbit/s

- دارای فیلترهای جانبی برای اتصال مستقیم به شبکه

- تطبیق با استانداردهای IEEE 802.3، IEEE 802.3u و IEEE 802.3ab

- پشتیبانی ازAUTO-MDIX

- پشتیبانی ازJTAG

- تغذیه 3V

- استفاده از تکنولوژی CMOS و توان مصرفی بسیار پایین

- محافظت در برابر ESD

- پکیجQFP

- LAN8710A

- پشتیبانی از سرعتهای 10 Mbit/s و 100 Mbit/s

- تطبیق با استانداردهای IEEE 802.3، IEEE 802.3u ، ISO 802-3

- پشتیبانی ازAUTO-MDIX ، Auto-negotiation

- ولتاژ تغذیه3 V ، رگولاتور 1.2 V باقابلیت غیرفعال سازی

- قابلیت تحمل ولتاژ 6 V بر روی پایههای I/O

- پکیج 32 پایه QFN

- LAN8720

- پشتیبانی از سرعتهای 10Mbit/s و 100Mbit/s

- تطبیق با استانداردهای IEEE 802.3، IEEE 802.3u

- پشتیبانی از AUTO-MDIX

- استفاده از تغذیه 3V با رگولاتور داخلی 1.2V یا ولتاژ تغذیه 1.2V بدون رگولاتور داخلی

- قابلیت تحمل ولتاژ 6V بر روی پایههای I/O

- پکیج 24 پایه QFP

تراشه های tranciver معمولاً دارای تعدادی رجیستر برای انجام تنظیمات اولیه هستند. از این تنظیمات میتوان به تنظیم استاندارد مورد استفاده، سرعت ارتباط، فعالسازی Auto-Negotiation ، آدرس PHY و … اشاره نمود.