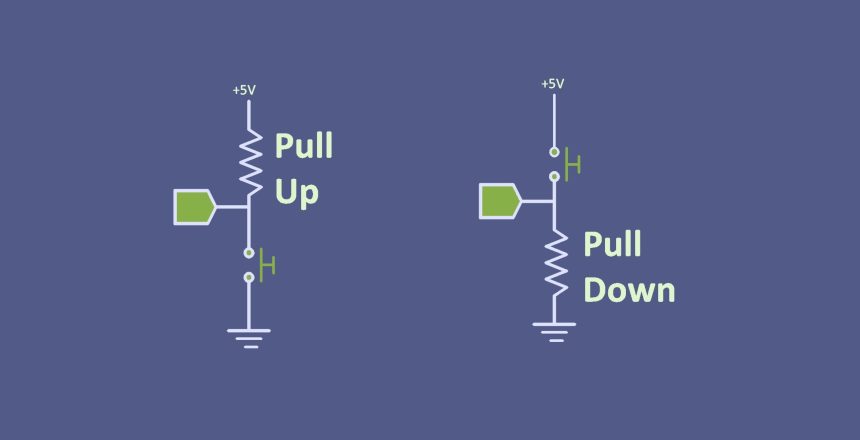

مقاومتهای pull-up (پول آپ) و pull-down برای بایاس درست ورودی های گیت های دیجیتال به کار میروند. همچنین استفاده از این مقاومتها باعث میشود تا ورودی، هنگامی که تغییراتی در سیگنال کنترل رخ نمیدهد دچار نوسان نشود .

گیتهای منطقی دیجیتال میتوانند به مدارات خارجی نیز اتصال یابند اما ابتدا باید اطمینان حاصل کنیم که ورودی و خروجی عملکرد درستی دارند و شرایط سوییچینگ درست را فراهم میکنند.

گیت های منطقی دیجیتال مدرن ، مدارات مجتمع (آی سی ها) و میکروکنترلرها شامل چندین ورودی و خروجی هستند که به آنها پین میگویند این رودی و خروجی ها باید به درستی (سطح بالا یا سطح پایین) تنظیم شوند تا مدار دیجیتال عملکرد درستی داشته باشد .

میدانیم که گیتهای منطقی کوچکترین جز سازندهی هر مدار منطقی دیجیتالی میباشد و با ترکیب ۳ گیت AND، OR و NOT میتوان اکثر مدارات ترکیبی پیچیده را به وجود آورد اما از آنجایی که این مدارات دیجیتال هستند تنها دو سطح منطقی دارند سطح منطقی صفر یا سطح منطقی یک .

اگر ورودی های یک گیت منطقی دیجیتال یا یک مدار در شرایطی نباشد که بتوان آنها را به عنوان ۰ یا ۱ منطقی مورد قبول دانست، ممکن است پالس اشتباه به مدار ارسال شود. به عنوان مثال ممکن است ولتاژ سطح بالای منطقی به اندازهی کافی بالا نباشد یا ولتاژ سطح پایین به اندازهی کافی پایین نباشد.

مدار الکتریکی که در شکل رو به رو نشان داده شده را در نظر بگیرید. دو سوییچ a و b ورودی های یک گیت منطقی هستند. هنگامی که سوییچ a بسته است (وضعیت روشن) ورودی A به زمین (0V) یا سطح منطقی پایین متصل شده و به همین شکل اگر سوییچ b بسته باشد ورودی B نیز به زمین متصل است و در سطح منطقی صفر قرار دارد این شرایط درست و دلخواه ما میباشد.

اما اگر سوییچ a باز شود چه اتفاقی میافتد؟ در این صورت چه ولتاژی به ورودی A میرسد؟ حال فرض کنیم که سطح ورودی A بالا (5V+) خواهد بود؛ از آن جایی که سوییچ a مدار باز شده ، ورودی A به زمین اتصال کوتاه نشده اما شرایط ورودی نامعلوم است چرا که به هیچ سطح ولتاژ قابل قبولی متصل نیست بنابراین به احتمال زیاد بین 0 تا 5V+ نوسان میکند.

این شرایط نامعلوم ممکن است باعث شود ورودی در نقطه A حتی در حالتی که کلید باز است نیز (پایین) باقی بماند در حالیکه ما انتظار داریم منطق یک (بالا) در نقطه A ایجاد شود. این شرایط ناپایدار و سیگنال ورودی ضعیف میتواند با کوچکترین نویز یا تداخلی تغییر کند و عملاً گیت غیرقابل استفاده میشود. چنین شرایطی ممکن است برای ورودی B نیز صادق باشد.

بنابراین به منظور جلوگیری از سوییچینگهای ناخواسه و ناگهانی مدارات دیجیتال، تمام ورودیهایی که به جایی متصل نیستند باید به منطق یک یا به منطق صفر متصل گردند ما میتوانیم این کار را به راحتی و با استفاده از مقاومتهای pull_up یا pull_down به انجام برسانیم تا پین ورودی یک حالت تعریف شده و مشخص داشته باشد

در هنگام ساخت مدارات الکترونیکی دیجیتال به احتمال زیاد با چند گیت باز مواجه میشوید و تمام ورودی های IC به کارتان نخواهد آمد این ورودی ها میتوانند به یکدیگر یا با استفاده از یک مقاومت با مقدار بالا به VCC متصل گردند ( در این شرایط مقاومت ، مقاومت pull-up نام دارد) حال اگر پایه IC با استفاده از یک مقاومت با مقدار پایین به زمین متصل شود این مقاومت ، مقاومت pull-down نام میگیرد. فراموش نکنید هرگز پایههای بلااستفادهی ورودی را به حال خود رها کنید.

مقاومت های پول آپ

این بار برای جلوگیری از نوسان ورودی A و B هنگامی که دو کلید A و B باز هستند، به منبع تغذیه 5V+ متصل میشوند. شاید تصور کنید این روش مشکل چندانی را به وجود نیاورد چرا که هنگامی که سوییچ a باز است، ورودی به VCC (5V+) متصل شده و هنگامی که سوییچ بسته است، ورودی به زمین اتصال پیدا کرده در نتیجه ورودی A و B صرف نظر از موقعیت سوییچ همیشه شرایط پیشفرض مشخصی را خواهد داشت.

اما این شرایط چندان مطلوب نیست چرا که اگر هر یک از سوییچ ها بسته باشد بین 5V+ تغذیه و زمین اتصال کوتاه به وجود میآید که در نهایت یا به سوختن فیوز و یا به آسیب دیدن مدار منتهی میشود برای غلبه بر این مشکل، باید یک مقاومت پول آپ بین پین ورودی و ۵+ ولت منبع تغذیه قرار گیرد.

کاربرد مقاومت pull-up

با استفاده از دو مقاومت pull-up هنگامی که سوییچ A یا سوییچ B باز هستند ورودی از طریق مقاومت pull-up به ۵ ولت متصل میشود در نتیجه جریان فوقالعاده کمی وارد ورودی گیت منطقی میشود و افت ولتاژ کمی در دو سر مقاومت pull-up رخ میدهد در نتیجه تقریباً ولتاژ 5V+ به پین ورودی اعمال میشود و منطق یک ساخته خواهد شد .

هنگامی که کلید A یاB بسته هستند، ورودی به زمین اتصال کوتاه میشود و سطح منطقی صفر به وجود خواهد آمد و مقاومت pull-up جریان فوقالعاده کمی را از طریق کلید بسته به زمین هدایت میکند.

در این شرایط ورودی همواره یک سطح منطقی معین دارد و بسته به باز یا بسته بودن سوییچ در سطح منطقی یک یا صفر به سر میبرد و از نوسان یا سلف بایاس ورودی جلوگیری شده که دقیقاً حالت کلیدزنی دلخواه و مورد نیاز ما میباشد.

حال شاید برای شما سؤال پیش بیاید که چگونه میتوانیم مقدار مقاومت مورد نیاز برای علمکرد صحیح مدار را محاسبه کنیم.

محاسبه مقدار مقاومت pull-up

تمام گیتهای منطقی دیجیتال و میکروکنترلرها نه تنها بر اساس ولتاژ کارکردشان محدود میشوند بلکه قابلیت سینک و سورس جریان توسط پایههای ورودی نیز آنها را محدودتر میکند.

مدارات منطقی دیجیتال در دو حالت باینری عمل میکنند که دو ولتاژ مجزا میباشد. ولتاژ سطح بالا یا (VIH) یا منطق یک و ولتاژ سطح پایین (VIL) یا منطق صفر. اما در بین این دو سطح ولتاژ ، سطوح دیگری وجود دارند که ممکن است توسط مدار به یکی از این دو سطح تعبیر شوند.

به عنوان مثال گیتهای منطقی سری 74LSxxx اختلاف پتانسیل ۲ ولت را به عنوان منطق یک تعبیر میکنند و اختلاف پتانسیل 0.8 ماکزیمم اختلاف پتانسیلی است که به عنوان منطق صفر تعبیر میشود.

به عبارتی دیگر در سری TTL 74LSxxx سیگنالهای ورودی بین 0 تا 0.8 سطح پایین تعبیر میشوند و سیگنال های ورودی بین 3 تا 5 ولت سطح بالا تعبیر میشوند و سطوح ولتاژی که بین 0.8 تا 2 قرار دارند؛ تعریف نشده هستند.

هنگامی که گیتهای منطقی به یکدیگر اتصال مییابند، جریان بین خروجی یکی از دروازههای منطقی ورودی دیگری حرکت میکند .مقدار جریانی که یک گیت منطقی TTL برای عملکردش به آن نیاز دارد، وابسته به سطح ولتاژ ورودی میباشد. برای سطح صفر پایههای تراشه منبع جریان هستند و برای سطح یک کشنده جریان.

هنگامی که سطح ورودی گیت منطقی بالا یک است جریان به ورودی TTL سرازیر میشود؛ چرا که مسیری است که به زمین متصل شده IH(MAX) مقداری مثبت میباشد چرا که به سمت گیت جریان پیدا کرده و در اکثر TTL های سری 74LSxxx جریان ورودی 20µA میباشد.

به همین صورت هنگامی که سطح ورودی یک گیت منطقی پایین است، جریان از ورودی TTL خارج میشود چرا که مسیری از ورودی به VCC ایجاد شده این جریان ورودی (IIL(MAX)) منفی است چرا که جریان از گیت خارج میشود و در اکثر TTL های سری 74LSxxx مقدار این جریان منفی 400µA (-0.4mA)- میباشد.

فراموش نکنید که سطح ولتاژ بالا و پایین و جریان بین سریهای مختلف TTL ها تفاوت دارد و ضمناً سطوح ولتاژ برای CMOS ها فوقالعاده پایینتر میباشد. در ضمن ولتاژ ورودی و جریان مورد نیاز برای میکروکنترلرها، PIC، آردوینو، رزبری پای (Raspberry Pie) و … نیز متفاوت خواهد بود بنابراین بهتر است ابتدا به دیتاشیت آنها نگاهی بیندازید .

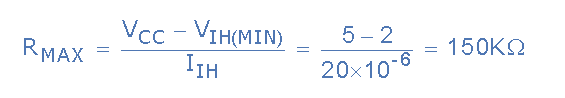

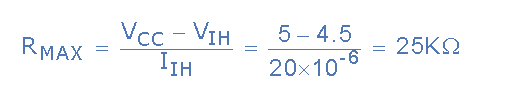

با دانستن مطالب بالا مقدار حداکثری مقاومت pull-up برای یکی از TTL74LS ها به صورت زیر محاسبه میشود :

محاسبه مقدار مقاومت pull-up برای گیت منطقی تک ورودی

سپس با استفاده از قوانین اهم، ماکزیمم مقاومت pull-up که ۳ ولت افت ولتاژ ایجاد میکند ۱۵۰kΩ خواهد بود. اما باید در نظر داشت که با انتخاب این مقاومت هیچ جایی برای اشتباه باقی نخواهد ماند چرا که افت ولتاژ دو سر مقاومت ماکزیمم است و جریان ورودی در مینیمم مقدار خود قرار دارد .

به صورت ایدهآل نیاز داریم تا سطح منطقی یک تا جای ممکن به VCC نزدیک باشد تا احتمال بروز خطا توسط دروازه های منطقی به حداقل برسد. بنابراین کاهش مقدار مقاومتی این مقاومت pull_up باعث میشود در صورت بروز افت ولتاژ در منبع تغذیه یا تلورانس مقاومت، خطا قابل چشمپوشی باشد و مدار دچار تشخیص اشتباه نشود. در هر صورت میزان مقاومت نیز نباید خیلی پایین باشد چرا که جریان عبوری از گیت افزایش مییابد و ممکن است سبب افزایش توان تلفاتی یا سوختن تراشه بشود.

بنابراین اگر بخواهیم دو سر مقاومت یک ولت افت ولتاژ داشته باشد و ۴ ولت به ورودی اعمال شود، باید از یک مقاومت 50KΩ استفاده کنیم انتخاب مقدار مقاومتی پایینتر افت ولتاژ را کاهش اما مقدار جریان را افزایش میدهد بنابراین همانطور که میبینید با وجود اینکه نمیتوان از هر مقاومتی به عنوان مقاومت pull-up استفاده کرد اما بازهی خیلی سخت و غیر قابل تغییری نیز برای انتخاب مقاومت وجود ندارد.

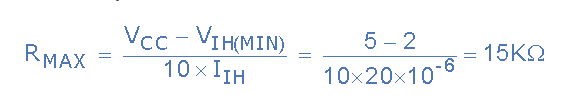

مثال بالا ماکزیمم مقدار مقاومت pull-up برای بایاس کردن یک گیت تکی TTL را به ما نشان میدهد اما استفاده از این مقاومت تنها به اینجا محدود نمیشود و به وسیله این مقاومت میتوان مدارات منطقی گوناگونی را در منطق یک بایاس کرد. به عنوان مثال فرض کنید یک مدار دیجیتال ساختهایم و ۱۰ ورودی گیت بلااستفاده در این مدار وجود دارد از آن جایی که ماکزیمم جریان ورودی یک دراوزه منطقی استاندارد TTL74LS بیست میکروآمپر است، ۱۰ گیت منطقی TTL ممکن است 10*200µA=20µA جریان نیاز داشته باشد.

بنابراین ماکزیمم مقدار مقاومتی برای یک مقاومت pull-up به منظور تغذیه ۱۰ ورودی بلااستفاده به صورت زیر محاسبه خواهد شد:

مقدار مقاومت pull-up برای چندین ورودی

حال اگر تعداد پایههای بلااستفاده ای که به یکدیگر متصل شدهاند را n در نظر بگیریم، جریانی که باید از مقاومت بگذرد: (n*IIHMAX) خواهد بود. اما هرگز نباید مقدار مقاومت را دقیقاً طوری تعیین کنید که حداقل جریان و افت ولتاژ مورد نیاز به گیت برسد چرا که منبع تغذیه نیز ممکن است با افت ولتاژ مواجه شود و در این صورت جریان پایهها تأمین نخواهد شد؛ بنابراین همیشه مقدار مقاومت pull-up را کمتر از مقدار محاسبه شده در نظر بگیرید.

مقاومت pull-up - مثال ۱

از دو گیت NAND TTL74LS00 به همراه یک سوییچ تک پل دو مسیره برای ساختن یک فلیپ فلاپ دو حالته ست ـ ریست (set-reset) استفاده شده حال مقدار زیر را محاسبه کنید:

۱) ماکزیمم مقامت pull-up اگر سطح ولتاژ ورودی بالا ( در حدود ۴/۵ ولت ) باشد و کلید باز است.

۲) جریانی که در حالتی که کلید بسته است از مقاومت عبور میکند.

۳) مدار را ترسیم کنید.

IIH(MAX)=2µA , VH=4.5V , VCC=5V

1- ماکزیمم مقدار مقاومت pull-up (RP(MAX))

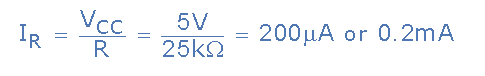

2- جریان مقاومت (IR)

مدار دو حالته ست ـ ریست (set-reset)

مقاومت pull-down

مقاومت pull-down (پول داون) درست همانند مقاومت pull-up (پول اپ) عمل میکند، با این تفاوت که این بار گیتهای منطقی به زمین متصل شدهاند و سطح ورودی گیت به صورت پیشفرض پایین است که با فشردن یک کلید مکانیکی بالا میرود.

مقاومت pull-down در مدارات دیجیتال مانند شمارنده ها و فلیپ فلاپ هایی که به یک سیگنال تحریک مثبت نیاز دارند کاربرد دارد در این حالت هنگامی که کلید فشرده میشود، حالت مدار نیز تغییر پیدا میکند.

ممکن است عملکرد مقاومت pull-down در نگاه اول مانند مقاومت pull-up باشد اما مقدار مقاومت pull-down خیلی پایینتر از مقاومت pull-up است در ضمن ورودی های TTL نسبت به CMOS در حالت سطح پایین جریان بیشتری را از خود عبور میدهند.

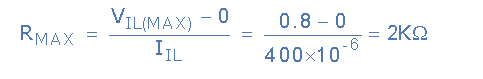

در گذشته بیان شد ماکزیمم سطح ولتاژی که به عنوان منطق صفر در TTL74LSxxx در نظر گرفته میشود ۰/۸ ولت خواهد بود (VL(MAX)=0/8V) همچنین هنگامی که سطح ورودی پایین است گیت به صورت سورس جریان عمل میکند و جریانی حدود 400µA از آن میگذرد ماکزیمم مقدار مقاومت pull-down برای یک گیت منطقی TTL تکی به صورت زیر محاسبه میشود :

مقدار مقاومت pull-down برای یک گیت منطقی

مقدار ماکزیمم مقاومت pull-down دو کیلو اهم میباشد. اما در اینجا نیز همانند محاسبه مقدار مقاومت pull-up باید مقداری تلورانس برای منبع تغذیه یا مقدار واقعی مقاومت در نظر گرفته میشود. به عنوان مثال اگر مقدار مقاومت خیلی بالا انتخاب شود، افت ولتاژ در دو سر مقاومت pull-down باعث میشود ولتاژ ورودی گیت بالاتر از بازه ی نرمال ورودی سطح پایین باشد و مدار دچار خطا شود. همچنین بهتر است مقدار ولتاژ ورودی کمتر از ۰/۵ ولت در نظر گرفته شود.

کاربرد مقاومت pull-down

بنابراین اگر ما تصور کنیم که روی دو سر مقاومت تنها ۰/۴ ولت افت ولتاژ خواهیم داشت با یک محاسبه کوتاه میتوانیم مقدار مقاومت pull-down ( در اینجا 1KΩ) را به دست بیاوریم .

کاهش بیشتر مقاومت منجر به افت ولتاژ کمتری میشود بر اساس دیتاشیت TLL های سری 74LSxxx حداقل جریان سطح پایین باید 0.4µA باشد.

همچنین اتصال ورودی ها به یکدیگر باعث عبور جریان بیشتری از مقاومت میشود به عنوان مثال اگر ۱۰ ورودی را به یکدیگر متصل کنیم ، 4mA جریان از مقاومت pull-down عبور میکند پس مقدار مقاومت pull-down مناسب 100Ω خواهد بود.

اما شاید با خود فکر کنید استفاده از مقاومت pull-down به چه دردی میخورد؟ چرا که شرایط اتصال مستقیم به زمین فراهم میباشد اما اتصال مستقیم به زمین بدون استفاده از مقاومت pull-down باعث میشود که جریان زیادی از پایه گیت منطقی عبور کند و همین امر سبب افزایش توان تلفاتی میشود. اما استفاده از مقاومت pull-down علاوه بر کاهش توان تلفاتی، منطق صفر را نیز برای ما به ارمغان میآرود.

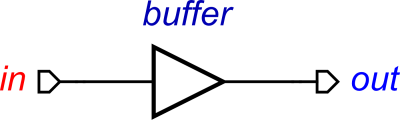

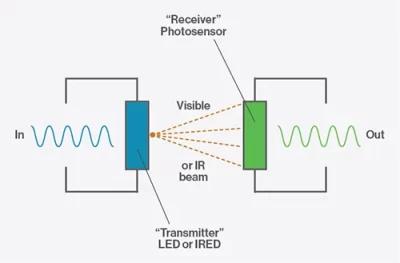

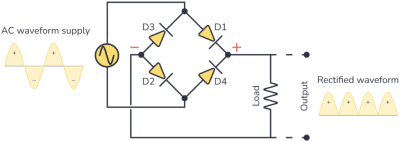

خروجی های کلکتور باز

همانطور که دیدیم میتوانیم از مقاومت pull-down و pull-up برای کنترل سطح ولتاژ یک دروازه ی منطقی بهره ببریم همچنین میتوان از مقاومت pull-up برای اتصال دروازه ی منطقی ها در انواع گوناگون به یکدیگر بهره برد به عنوان مثال میتوان یک دروازه منطقی CMOS را به TTL متصل نمود یا در خطوط انتقال که نیاز به جریان یا ولتاژ بالاتری دارند از آنها بهره برد .

برخی دروازه های منطقی طوری طراحی شدهاند که کلکتور آنها باز باقیمانده این حالت دیگر دراوزه منطقی خروجی را به سطح بالا نمیبرد و این وظیفه به دوش مقاومت pull-up گذارده شده .

به عنوان مثال TTL74LS01 که دارای دو گیت خروجی NAND کلکتور باز است .

کلکتور باز (OC) در ترانزیستورهای دو قطبی و درین باز در CMOS ها اجازه میدهند تا جریان خروجی بیشتری داشته باشیم همچنین میزان تلورانس ولتاژ نیز افزایش مییابد به عنوان مثال برای راه اندازی یک بار توان بالا مانند رله یا موتور DC از مقاومت pull-up به همراه دروازه منطقی کلکتور باز استفاده میشود .

هنگامی که یک مقاومت pull-up به کلکتور خروجی اتصال یافته خروجی همانند یک دروازه منطقی معمولی عمل میک ند یعنی هنگامی که خروجی ترانزیستور باز یا خاموش است سطح خروجی بالا میباشد و هنگامی که ترانزیستور روشن میشود سطح خروجی پایین میآید به عبارتی دیگر ترانزیستور روشن میشود تا خروجی را به سطح پایین بکشاند. اندازهی مقاومت pull-up وابسته به باری که به آن متصل شده و افت ولتاژ دو سر مقاومت در هنگامی که ترانزیستور خاموش است دارد.

هنگامی که سطح خروجی پایین است، ترانزیستور باید قادر باشد تا جریان بار را از طریق مقاومت pull-upبه سمت خود بکشاند به همین صورت هنگامی که سطح خروجی بالا است جریانی که از مقاومت pull-up میگذرد باید بهقدری بالا باشد تا بتواند بار متصل به دروازه ی منطقی را کنترل کند .

همانطور که در گذشته دیدیم خروجی یک دروازه ی منطقی دیجیتال همانند ورودی در دو حالت باینری عمل میکند که این دو حالت با دو ولتاژ مجزا تعریف میشود ولتاژ سطح بالا VH یا منطق یک و ولتاژ سطح پایین VL یا منطق صفر .

VOH(MIN) حداقل ولتاژ خروجی است که میتواند توسط مدار به عنوان منطق یک تعبیر شود و برای TTL این اختلاف پتانسیل ۲/۷ ولت میباشد VOL(MAX) نیز ماکزیمم ولتاز خروجی است که میتواند به عنوان منطق صفر تعبیر شود و برای TTL این مقدار ۰/۵ ولت خواهد بود به عبارتی دیگر در سری TTL74LSxxx اختلاف پتانسیل بین ۰ تا ۰/۵ ولت سطح پایین تعبیر میشود و ولتاژ های خروجی بین ۲/۷ تا ۵ ولت سطح بالا هستند.

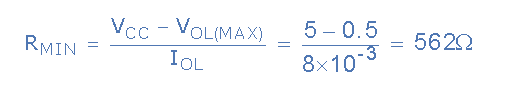

بنابراین هنگامی که از گیتهای منطقی کلکتور باز استفاده میکنید ، مقدار مقاومت pull-up توسط معادلات زیر تعیین میشود :

مقدار مقاومت pull-up کلکتور باز

یک گیت NAND کلکتور باز دارای مقادیر زیر میباشد:

VCC=5V , VOL=0.5V ,IOL(MAX)=8mA فراموش نکنید محاسبه درست مقاومت pull-up از اهمیت زیادی برخوردار است و جریانی که از مقاومت pull-up میگذرد نباید از IOL(MAX) تجاوز کند.

در گذشته گفته شد که گیتهای منطقی کلکتور باز برای راه اندازی بارهایی به کار میروند که نیاز به سطوح ولتاژ و جریان بالاتری دارند مانند موتورهای DC قطعه TTL741506 دارای IOL(MAX) چهل میلی آمپری میباشد و مقدار VOH(MAX) برای این قطعه ۳۰ ولت است ( فراموش نکنید که خود IC باید از منبع تغذیه ۵ ولتی استفاده کند سپس 74LS06 به ما اجازه میدهد تا یک بار را که به جریان های بالا ( حداکثر تا ۴ میلی آمپر ) نیاز دارد را راه اندازی کنیم.

مقاومت pull-up - مثال 2

برای کنترل یک نشانگر led قرمز به یک درایور معکوس کننده 74LS06 و یک منبع تغذیه ۱۲ ولتی نیاز است. اگر در افت ولتاژ ۱/۷ ، LED به ۱۵ میلی آمپر جریان نیاز داشته باشد و VOL قطعه در حالت اشباع ۰/۱ ولت باشد، مقدار مقامت محدود کننده جریان برای راه اندازی LED را محاسبه کنید.

ما میتوانیم که از درایورهای کلکتور باز به همان صورت قبلی برای راه اندازی بارهای توان بالایی مانند رله های الکترومکانیکی، لامپ یا موتورهای DC نیز بهره ببریم. این المانها برای علمکرد درست به ولتاژی بین ۵ تا ۱۲ ولت و جریانی بین ۲ تا ۱۰ میلی آمپر نیاز دارند.

۲ یا چند خروجی کلکتور باز گیتهای TTL میتواند به صورت مستقیم به یکدیگر متصل شوند و همگی از یک مقاومت pull-up خارجی استفاده کنند. در نتیجه خروجی ها طوری با یکدیگر تعامل دارند که انگار به یک گیت AND متصل شدهاند. این نوع پیکربندی سیستم سیم کشی AND نام دارد.

خلاصه مقاومت پول آپ

- در این مقاله مشاده کردیم هنگامی که از مقاومت pull-up یا pull-down استفاده نشود ورودی دراوزه منطقی دیجیتال ممکن است سلف بایاس یا دچار نوسان شود و در نتیجه مدار با خطاهای کلیدزنی بسیاری مواجه شود. چرا که پایههای ورودی بدون اتصال به نقطهای به حال خود رها شدهاند.

- یک مقاومت pull-up به پایههای ورودی بلااستفاده ( گیت های AND و NAND متصل میشود و آنها را به VCC پیوند میزند تا سطح ورودی بالا باقی بماند. همچنین یک مقاومت pull-down پایههای بلااستفاده از گیت های OR و NOR را به زمین ( صفر ولت ) پیوند میزند تا مقدار ورودی را پایین نگه دارد.

- مقدار مقاومت pull-up جای تلورانس دارد اما باید طوری انتخاب شود تا ولتاژ پایه ورودی را بالای VIH نگه دارد استفاده از مقاومتهای 10KΩ رایج است اما مقدار مقاومت pull-up میتواند از 1KΩ تا 10KΩ تغییر کند.

- مقاومتهای pull-down بازه بستهتری نسبت به مقاومتهای pull-up دارند چرا که سطح ولتاژ ورودی پایین است و جریان IH بیشتری دارد استفاده از مقاومت pull-down صد اهمی بسیار رایج است. اما مقدار مقاومت pull-down میتواند بین ۵۰Ω تا ۱KΩ تغییر کند.

- گیتهای منطقی دیجیتال کلکتور باز (برای ترانزیستورهای دو قطبی TTL) و درین باز برای ترانزیستور های ماسفت (CMOS) نیاز دارد تا به یک مقاومت pull-up خارجی بین پین های خروجی و منبع تغذیه DC متصل شود تا گیت های منطقی قادر باشد عملکرد درستی داشته باشد.

- مزایای استفاده از گیتهای درین / کلکتور باز توانایی آنها برای کلیدزنی در ولتاژ و جریان های بالا میباشد در ضمن این گیت ها میتوانند طوری به یکدیگر متصل شوند که انگار به یک عملگر AND اتصال یافتهاند برخی گیت های کلکتور باز مانند 74LS06 قادر هستند بارهای بزرگتری را راه اندازی کنند چرا که خروجی شان میتواند به وسیله یک مقاومت پول آپ خارجی به منبع تغذیه بالای ۳۰ ولت متصل شود.