فهرست مطالب

تعریف ولتاژ آفست ورودی

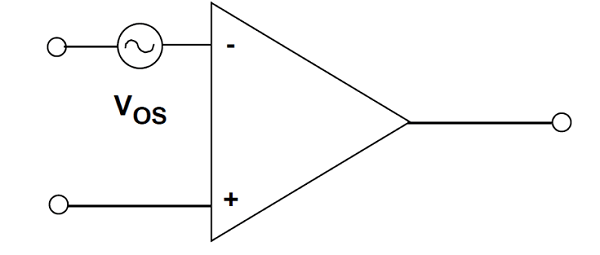

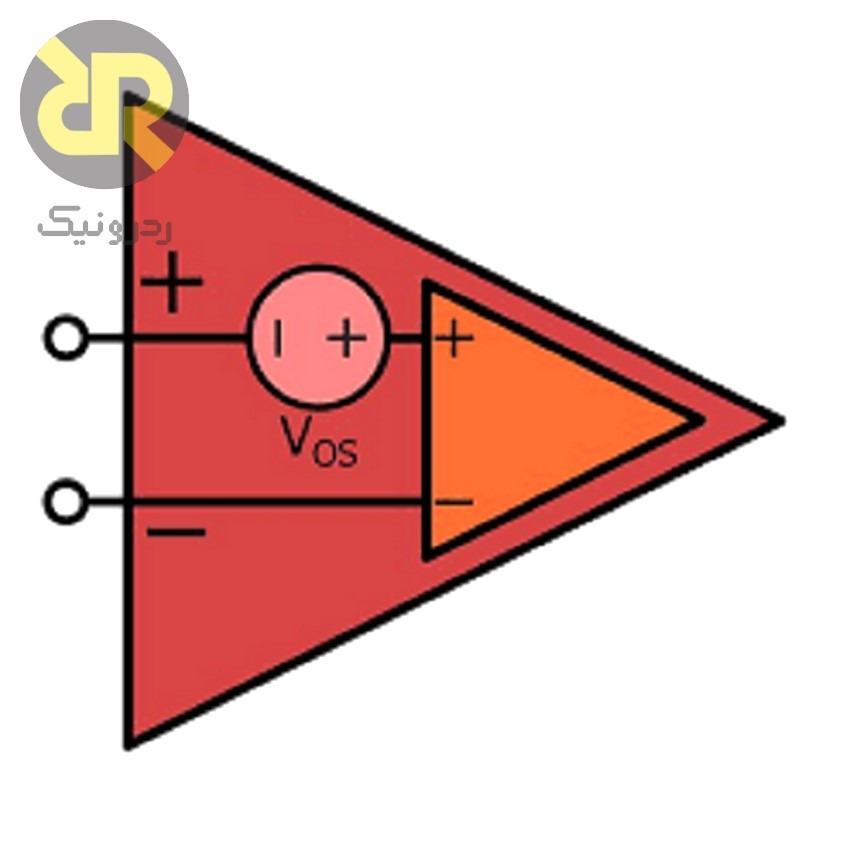

بهطور ایدهآل، اگر هر دو ورودی آپامپ دقیقا در ولتاژ مشابه باشند، خروجی باید صفر باشد. در عمل، یک ولتاژ تفاضلی کوچک باید به ورودیها اعمال شود تا خروجی صفر شود. این ولتاژ بهعنوان ولتاژ آفست ورودی، Vos، شناخته میشود. ولتاژ آفست ورودی بهصورت یک منبع ولتاژ Vos مدل سازی میشود. همانطورکه در شکل.1 نشان داده شده است این منبع با پایانه ورودی معکوسکننده آپامپ سری است.

- ولتاژ آفست: ولتاژ تفاضلی که به باید به ورودی آپامپ اعمال شود تا خروجی صفر شود. در زیر دامنه ولتاژ آفست ورودی برخی از انواع آپ امپ بیان شده است:

- آپامپهای برشگر پایا: < 1 میکرو ولت

- آپامپهای دقیق همه منظوره: میکروولت 500-50

- بهترین آپامپهای دوقطبی: میکرو ولت 25-10

- بهترین آپامپهای ورودی JFET: میکرو ولت 100-1000

- آپامپهای سرعت بالا: میکرو ولت 2000-100

- آپامپ CMOS تنظیمنشده:میکرو ولت 50000-5000

- آپامپهای CMOS سری DigiTrim : < میکرو ولت 1000-100

Vos آپامپهای برشگر پایا (صفر خودکار نیز نامیده میشوند برای مثال، AD8538، AD8551، AD8571،AD8628، AD8630) کمتر از 1 میکرو ولت است، و بهترین آپامپهای دو قطبی دقیق (بایاس پایا یا ضریب تقویت بزرگ) میتوانند حداکثر آفست 25 میکروولت داشته باشند (OP177F). بهترین انواع ورودیJFET تنظیمشده، آفستی در حدود 100میکرو ولت دارند (AD8610B، AD8620B)، و آفست آپ امپهای CMOS تنظیمنشده میتواند از 5 تا 50 میلی ولت تغییر کند.

با اینحال، آپامپهای CMOS سری ADI با تنظیم دیجیتالی دقیق ولتاژهای آفستی کمتر از 100 میکروولت دارند (برای مثال، AD8603، AD8607، AD8608، AD8606، AD8609, AD8606 ). بطورکلی، آپامپهای «دقیق» Vos کمتر از 0.5 میلی ولت دارند. اگرچه برخی تقویتکنندههای سرعت بالا ممکن است کمی بدتر از این باشند. فرآیند تنیظم دیجیتالی بعدا در این آموزش توضیح داده خواهدشد.

رانش ولتاژ آفست ورودی و اثرات فرسودهسازی

ولتاژ آفست ورودی با دما تغییر میکند، و ضریب دمای آن TCVos یا بطور متدوالتر، رانش نامیده میشود. رانش آفست تحت تاثیر تنظیمات آفست آپامپ قرار میگیرد، اما زمانیکه ولتاژ آفست یک آپامپ با ورودی دوقطبی حداقل شود، رانش ممکن است تا 0.1μV/°C. کاهش پیدا کند (مقدار متعارف برای OP177F ). مقادیر رانش متعارفتر برای یک گستره از آپامپهای دقیق همه منظوره در گستره μV/°C 1-10 قرار دارند. بیشتر آپامپها یک مقدار TCVos مشخص دارند، اما برخی، در عوض، دومین مقدار حداکثر Vos را دارند که در سرتاسر محدوده دمای عملکرد تضمین میشود. چنین ویژگی کمتر مفید است، زیرا هیچ تضمینی وجود ندارد که TCVos ثابت یا یکنواخت باشد.

همچنین ولتاژ آفست با گذشت زمان تغییر میکند، یا فرسوده میشود. بطور کلی، فرسودهسازی بهصورت میکروولت بر ماه (μV/month) یا میکروولت بر 1000 ساعت مشخص میشود، اما این موضوع میتواند گمراهکننده باشد. از آنجاییکه فرسودهسازی یک پدیده «تصادفی» است، متناسب با ریشه دوم زمان سپریشده است.بنابراین نرخ فرسودهسازی 1 میکروولت بر 1000 ساعت در حدود 3 میکروولت بر سال (نه 9 میکروولت بر سال) میشود.

پایداری طولانی مدت OP177F درحدود 0.3μv/month است. این به یک دوره زمانی پس از 30 روز اول کار اشاره میکند. به استثنای ساعت اولیه کار، تغییرات در ولتاژ آفست این قطعات در طول 30 روز اول معمولا کمتر از 2μv هستند.

پایداری طولانی مدت آپامپهای برشگر پایا مشخص نیست زیرا مدار خودکار صفر هرگونه آفست ناشی از فرسودهسازی را از بین میبرد.

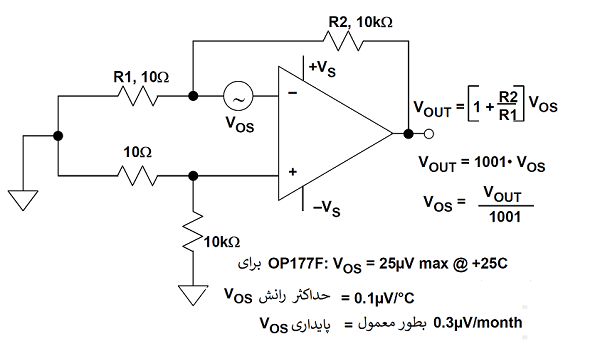

اندازهگیری ولتاژ آفست ورودی

اندازهگیری ولتاژهای آفست ورودی در حدود چند میکروولت مستلزم آن است که مدار آزمایش خطایی بیشتر از ولتاژ آفست خودش وارد نکند. شکل 2 یک مدار استاندارد برای اندازهگیری ولتاژ آفست را نشان میدهد. این مدار ولتاژ آفست ورودی را با بهره نویز 1001 تقویت میکند. اندازهگیری در خروجی تقویتکننده با استفاده از یک ولتمتر دیجیتال دقیق انجام میشود. این ولتاژ آفست ورودی (RTI) با تقسیم ولتاژ خروجی بر بهره نویز محاسبه میشود. مقاومت منبع کوچکی که توسط ورودی مشاهده میشود منجر به سهم ناچیز جریان بایاس در ولتاژ آفست اندازهگیریشده میشود. برای مثال، جریان بایاس 2 نانوآمپر که در مقاومت 10 اهمی جریان مییابد یک خطای 0.02μv را در ورودی تولید میکند.

با وجود سادگی، این مدار به آسانی میتواند در هنگام آزمایش آپامپهای دقیق نتایج غیردقیق بدهد، مگر اینکه در اجرا دقت شود. بزرگترین منبع خطای احتمالی در اتصالات ترموکوپل پارازیتی بوجود میآید، جاییکه دو فلز مختلف به هم متصل شدهاند. این ولتاژ ترموکوپل میتواند گستره از 2μv/°c تا بیش از 40μv/°c داشته باشد. توجه داشته باشید که در این مدار مقاومتهای «ساختگی» اضافی به ورودی غیرمعکوسکننده متصل شدهاند، تا دقیقا متعادلکننده یا تطبیق دهنده اتصالات ترموکوپل در مسیر ورودی معکوسکننده باشند.

همچنین دقت اندازهگیری به طرح مکانیکی اجزا و چگونگی قرارگیری دقیق آنها برروی برد PC بستگی دارد. به خاطر داشته باشید که دو اتصال یک جز همانند یک مقاومت، دو ولتاژ ترموکوپل یکسان ولی با قطبیت مخالف ایجاد میکنند (فرض میشوند که آنها به فلز مشابه مثل مسیر مسی بر روی یک برد PC متصل میشوند). با این فرض که هر دو دقیقا در دمای مشابه هستند، اینها یکدیگر را خنثی میکنند. اتصالات کامل و طولهای کوتاه سرب به حداقل کردن تغییرات دما و افزایش دقت اندازهگیری کمک میکنند.

در این مدار آزمایشی، جریان هوا باید حداقل باشد تا اتصالات ترموکوپل در دمای مشابه ثابت شوند. در برخی موارد، این مدار باید در یک محفظه بسته کوچک قرار بگیرد تا تاثیرات جریانهای هوای خارجی را حذف کند. این مدار باید ثابت برروی یک سطح قراربگیرد تا جریانهای همرفتی بر بالای برد نه در امتداد اجزا ( مثل نصب صفحه به صورت عمودی) سرازیر و جاری شوند.

اندازهگیری تغییر ولتاژ آفست با دما چالشی دشوار است. قرارگیری برد مدار چاپی دربرگیرنده تقویتکننده در حال آزمایش در یک جعبه یا کیسه پلاستیکی کوچک با عایقی با حبابهای ریز، مانع ایجاد جریان هوای محفظه دما در اثر تغییرات حرارتی در آن سوی ترموکوپلهای پارازیتی میشود. در صورت نیاز به آزمایش سرما تصیفه نیتروژن خشک توصیه میشود. چرخه دمایی متمرکز تقویتکننده با استفاده از یک خنککننده یا گرمکننده نوع جریان حرارتی ممکن است راه دیگری باشد، با اینحال این واحدها تمایل به تولید مقدار زیادی جریان هوا دارند که میتواند مشکلساز باشد. بطورکلی، مدار آزمایشی شکل 2 میتواند برای کار در بسیاری از تقویتکنندهها ساخته شود. مقادیر مطلق کم برای مقاومتهای کوچک (مانند 10 اهم) خطاهای ناشی از جریان بایاس را به حداقل میرسانند.

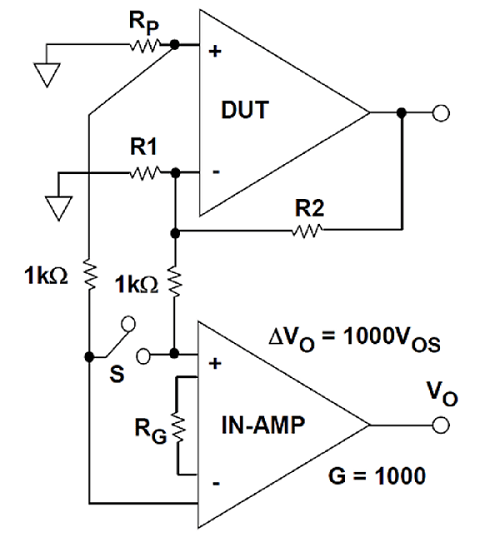

روش اندازهگیری یک Vos متناوب در شکل 3 نشان داده شده است، و برای جریانهای بایاس بالا و یا نامساوی مناسب است (مانند آپامپهای فیدبک جریان). در این روش اندازهگیری، یک تقویتکننده ابزارگزینی از طریق مقاومتهای جداساز به پایانههای ورودی آپامپ متصل میشود، و بهره را برای اندازهگیری فراهم میکند. ولتاژ آفست تقویتکننده (اندازهگیریشده با S بسته) باید از اندازه نهایی Vos کم شود.

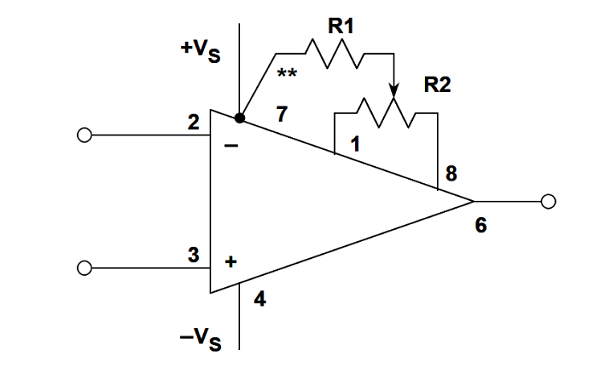

تنظیم ولتاژ آفست با استفاده از پایههای «صفر»

بسیاری از آپامپهای منفرد پایههایی برای صفر آفست عملیاتی دارند. برای ایجاد این ویژگی، دو پایه با یک پتانسیومتر بهم متصل میشوند، و همانطورکه در شکل 4 نشان داده شده است لغزنده از طریق یک مقاومت به یکی از منابع میرود. توجه داشته باشید که اگر لغزنده بصورت اتفاقی به منبع اشتباه متصل شود، آپامپ احتمالا آسیب خواهد دید-این یک مشکل وقتی یک نوع آپامپ با نوع دیگری جایگزین میشود متداول است. گستره تنظیم آفست در یک آپامپ با طراحی خوب برای حداقل کردن حساسیت، بیش از دو یا سه برابر حداکثر Vos کمترین درجه دستگاه نیست. ضمنا، بهره ولتاژ یک آپامپ در پایههای تنظیم آفست ممکن است در حقیقت بزرگتر از بهره در ورودیهای سیگنال است! بنابراین بسیار مهم است که این پایهها بدون نویز باقی بمانند. توجه داشته باشید که استفاده از بارهای بزرگ از یک آپامپ به یک پتانسیومتر صفرکننده از راه دور هرگز توصیه نمیشود.

- اتصال لغزنده با توجه به آپامپ میتواند به VS+ یا VS – باشد.

- مقادیر R به آپامپ بستگی دارد. به دیتاشیت مراجعه کنید.

- ولتاژ آفست ورودی را خنثی کنید نه آفستهای سامانه!

- ممکن است بهره بالایی از پایههای آفست به خروجی وجود داشته باشد-آنها را ثابت نگه دارید!

- آفست صفرکننده سبب افزایشی در ضریب دمایی آفست میشود، تقریبا 4μv/ºc برای 1 میلی ولت صفر آفست برای ورودیهای FET.

همانطورکه در بالا بیان شد، رانش آفست یک آپامپ با میزانسازی تنظیمات آفست آن با دما تغییر خواهدکرد. بنابراین پایانههای تنظیم داخلی باید تنها برای تنظیم آفست خود آپامپ استفاده شوند نه برای اصلاح خطای آفست سامانه، زیرا این کار موجب افزایش رانش دما میشود. تاوان رانش برای یک آپامپ ورودی FET، در حدود 4μv/ºcبرای هر 1 میلی ولت ولتاژ آفست صفر است. بطورکلی بهتر است ولتاژ آفست را با انتخاب مناسب دستگاه یا درجه کنترل کنیم.

تنظیم آفست (روشهای خارجی)

اگر یک آپامپ پایههای تنظیم آفست نداشته باشد (آپامپهای دو پایه متداول یا تمام آپامپهای چهارپایه پایه تنظیم آفست ندارند)، و تنظیم آفستهای تقویتکننده و سامانه ضروری باشد، یک روش خارجی میتواند بکاربرده شود. همچنین این روش درصورتیکه تنظیم آفست با یک ولتاژ قابل برنامهریزی سامانه، مثل DAC انجام شود بسیار مفید خواهدبود.

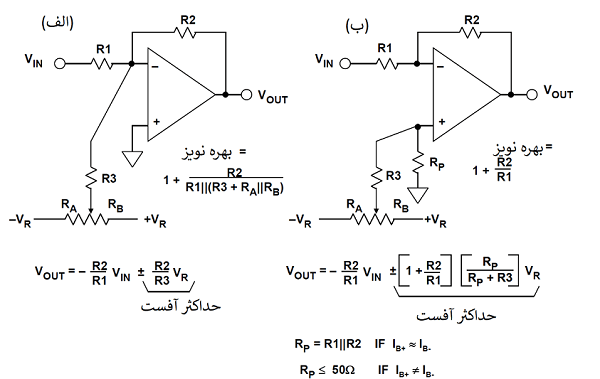

با یک پیکربندی آپامپ معکوسکننده، تزریق جریان به ورودی معکوسکننده همانطورکه در شکل 5الف نشان داده شده است، سادهترین روش است. نقطه ضعف این روش این است که به دلیل مسیر موازی R3 و مقاومت پتانسیومتر، کمی افزایش در بهره نویز امکانپذیر است. این افزایش بهره نویز ممکن است با ایجاد مقادیر بزرگی از ±VRکاهش یابد از اینرو مقدار R3 بسیار بزرگتر از R1||R2 است. توجه داشته باشید که منابع توان ثابت و فاقد نویز هستند، از آنها میتوان بهعنوان VR± استفاده کرد.

شکل 5ب چگونگی پیادهسازی تنظیم آفست از طریق تزریق یک ولتاژ آفست کوچک به ورودی غیرمعکوسکننده را نشان میدهد. این مدار به 5الف ترجیح داده میشود، زیرا منجر به افزایش بهره نویز میشود (اما نیاز به اضافه کردن مقاومت RP دارد). اگر آپامپ به جریانهای بایاس ورودی متصل شود، RP باید برابر R1||R2 باشد (برای حداقل کردن ولتاژ آفست افزوده شده).

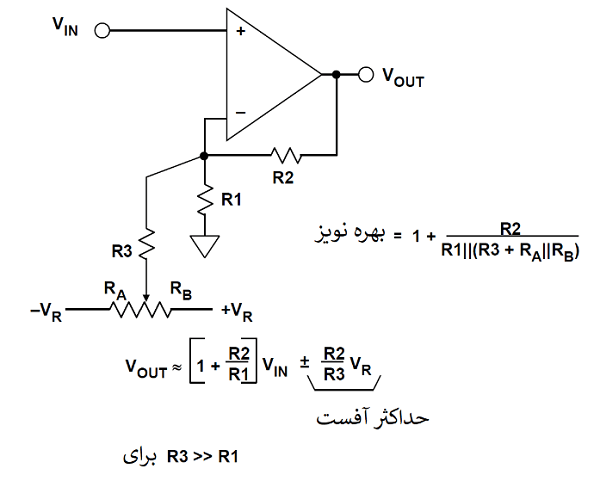

در هنگام استفاده از آپامپ در حالت غیرمعکوسکننده میتوان از مدار نشان داده شده در شکل 6 برای تزریق یک ولتاژ آفست کوچک استفاده کرد. این مدار برای آفستهای کوچک بخوبی کار میکند، در اینجا R3 میتواند بسیار بزرگتر از R1 باشد. توجه داشته باشید که در غیراینصورت، تنظیم پتانسیومتر آفست ممکن است بر بهره سیگنال اثر بگذارد. بههرحال، اگر R3 به منابع ولتاژ مرجع امپدانس پایین ثابت، VR± متصل شود، بهره حاصل می شود.

فرآیندهای تنظیم ولتاژ آفست

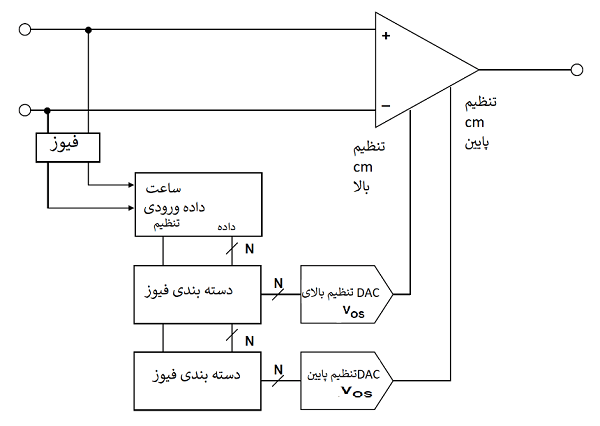

خانواده آپ امپ CMOS تنظیم دیجیتالی (DigiTrim™) از مزایای فنآوری دیجیتال بهره میبرد، به گونهای که ولتاژ آفست مرتبط با تقویتکنندههای CMOS را معمولا حداقل میسازد. تنظیم ولتاژ آفست پس از بستهبندی دستگاهها انجام میشود. یک کد دیجیتالی برای تنظیم ولتاژ آفست به کمتر از 1 میلیولت، بسته به درجه، به دستگاه داده میشود. آزمایش ویفر الزامی نیست، و روش دستگاههای آنالوگ ثبتشده که DigiTrim™ نامیده میشود به پایههای اضافی برای اجرای عملکرد نیازی ندارد. این دستگاهها ورودیها و خروجیهای ریل به ریل هستند، و طبقههای ورودی موازی NMOS و PMOS بطور جداگانه با استفاده از DigiTrim برای حداقل کردن ولتاژ آفست در هر دو جفت تنظیم میشوند. یک طرح کارکردی از آپامپ CMOS DigiTrim نوعی در شکل 7 نشان داده شده است.

μμDigiTrim ولتاژ آفست را با برنامهریزی منابع جریان وزندار بصورت دیجیتالی تنظیم میکند. اطلاعات تنظیم از طریق پایههای موجود با استفاده از یک دنباله دیجیتالی خاص وارد میشوند. مقادیر تنظیم میتوانند برای دقت بهینه پیش از انجام تنظیم نهایی بطور موقت برنامهریزی، ارزیابی و باز اصلاح شوند. پس از تکمیل تنظیم، مدار تنظیم برای جلوگیری از احتمال هر تنظیم تصادفی مجدد توسط کاربر نهایی قفل میشود.

تنظیم فیزیکی که با سوزاندن فیوزهای پلیسیلیکن حاصل میشود بسیار قابل اطمینان است. هیچ پد یا پایه اضافی، و تجهیزات ویژ*ه آزمایش برای تنظیم لازم نیست. تنظیمات میتوانند پس از بستهبندی انجام شوند تا جابجاییهای مربوط به مونتاژ از بین بروند. به دلیل بازدهی بالای قرص نیمه رسانا، آزمایش در سطح ویفر موردنیاز نیست.

اولین دستگاههایی که از این روش استفاده میکنند دستگاههای آنالوگ تقویتکننده CMOS ریل تو ریل AD8601, AD8602, AD8604 (تک، دوتایی، چهارتایی) هستند. این آفست برای هر دو وضعیت حالت مشترک پایین و بالا تنظیم میشود تا ولتاژ آفست در گستره کامل ولتاژ ورودی حالت مشترک زیر 500μv باشد. پهنای باند آپامپها 8 مگاهرتز است، سرعت تغییر خروجی 5v/μs است، و جریان منبع در هر تقویتکننده فقط 640 میکروآمپر است.

خانواده AD8603, AD8605, AD8607 (تک، دوتایی، چهارتایی) در گستره کامل حالت مشترک ولتاژهای آفست حداکثر را با حداکثر 50μv دارد. پهنای باند 400 کیلوهرتز است، و جریان منبع در هر تقویتکننده تنها 50 میکروآمپر است

در این مرحله مرور دیگر روشهای برش متداول مفید است. دستگاههای آنالوگ در استفاده از مقاومتهای لایه نازک و برش ویفر لیزری برای تقویتکنندههای دقیق، منابع، مبدلهای داده، و دیگر مدارهای مجتمع خطی پیشگام بودند. دقت تا 16 بیت میتواند با برش بدست آید، و مقاومتهای لایه نازک خودشان نسبت به دما پایدار هستند و میتوانند پایداری حرارتی و دقت یک دستگاه را حتی بدون تنظیم افزایش دهند. لایه نشانی لایه نازک و الگودهی فرآیندهایی هستند که باید کاملا کنترلشده باشند. همچنین سامانههای تنظیم لیزری تقریبا گرانقیمت هستند. در بستهبندی تنظیم غیرممکن است، بنابراین جابجاییهای مرتبط با مونتاژ نمیتوانند به آسانی ترمیم شوند. ضمنا، تنظیم لایه نازک در سطح ویفر در مدارهای مجتمع دقیق که به دقت و پایداری بالا نیاز دارند وضوح تنظیم خوب و مداوم را فراهم میکند.

شکست زنری از یک ولتاژ برای ایجاد یک اتصال کوتاه فلزی در امتداد پیوند بیس-امیتر یک ترانزیستور برای حذف یک جز مدار استفاده میکند. پیوند بیس-امیتر معمولا به یک زنر اشاره میکند، اگرچه این سازوکار در حقیقت شکست بهمنی این پیوند است. در طی شکست بهمنی در امتداد پیوند بیس-امیتر، چگالیهای جریان بسیار بالا و حرارت موضعی مهاجرت فلزی سریع را بین اتصالهای بیس و امیتر تولید میکند، که منجر به یک اتصال کوتاه فلزی در امتداد پیوند میشود. با بایاس مناسب (جریان، ولتاژ، و زمان)، این اتصال کوتاه مقدار مقاومت بسیار پایینی دارد. اگر یک سری از این پیوندهای بیس-امیتر به موازات یک رشته از مقاومتها قراربگیرند، پیوندهای اتصال کوتاه انتخاب شده بخشهایی از رشته مقاومتی را اتصال کوتاه خواهند کرد، بنابراین مقدار مقاومت کلی تنظیم میشود.

ممکن است تنظیم شکست زنری در بستهبندی IC برای جبران جابجاییهای مرتبط با مونتاژ در ولتاژ آفست انجام شود. به هرحال، تنظیم در بستهبندی به پایههای پکیج اضافی نیاز دارد. از طرف دیگر، تنظیم در سطح ویفر به پدهای پروب اضافی نیاز دارد. پدهای پروب با کاهش مشخصات فرآیند به بهترین نحو تنظیم نمیکنند. بنابراین سطح قرص نیمه هادی موردنیاز برای تنظیم بدون درنظرگرفتن هندسه فرآیند، تقریبا ثابت است. شکلی از ترانزیستور دوقطبی برای ساختارهای تنظیم شده موردنیاز است، بنابراین یک فرآیند کاملا مبتنی بر MOS قابلیت شکست زنری ندارد. از آنجاییکه حذف یک جز مدار یک مقدار مقاومت از پیش تعریفشده را از بین میبرد ماهیت این تنظیمات گسسته است. افزایش وضوح تنظیم نیاز به ترانزیستورها و پدها یا پینهای اضافی دارد،که به سرعت سطح کلی قرص نیمههادی و/یا هزینه بستهبندی را افزایش میدهند. این روش موثرین روش برای فرآیندهای با هندسه نسبتا بزرگ است، چنانکه ساختارهای بریده شده و پدهای پروب درصد نسبتا کوچکی از کل سطح قرص نیمه هادی را اشغال میکنند.

در 1975 این روش بخشی از فرآیند ایجاد استاندارد صنعتی OP07 بود فرآیندی که در آن یکپارچهسازی دقیق پیشتاز تنظیم حذف زنری بود. OP07 و دیگر قسمتهای مشابه باید بتوانند با منابع بیش از 15V± کارکنند. در نتیجه، آنها از هندسههای دستگاه نسبتا بزرگ استفاده میکنند تا الزامات ولتاژ بالا را تحمل کنند، و پدهای پروب اضافی سطح قرص نیمههادی را بطور قابل توجهی افزایش نمیدهند.

تنظیم پیوندی قطع پیوندهای فلزی یا پلی سیلیکنی به منظور حذف یک اتصال است. در تنظیم پیوندی، یک لیزر یا یک جریان بالا برای تخریب یک اتصال «کوتاه» در امتداد یک جز مقاومتی موازی بکاربرده میشود. حذف اتصال مقاومت موثر جز (اجزای) ترکیبشده را افزایش میدهد. قطع لیزری مشابه تنظیم لیزری لایه نازک کار میکند. حرارت موضعی بالا از باریکه لیزری موجب تغییرات ماده میشود که منجر به یک ناحیه نارسانا، قطع یک فلز یا رابط پلی سیلیکن رسانا بطور کارآمد میشوند.

روش تنظیم دقیق پیوندی جریان بالا به عنوان معکوس اتصال کوتاه زنری عمل میکند- این اتصال رسانا تخریب میشود، در عوض با یک حذف زنری تولید میشود.

ساختارهای تنظیم پیوندی نسبت به ساختارهای مقاومتی تنظیم شده با لیزر تا حدی فشردهتر هستند. بطورکلی هیچ فرآیند خاصی مورد نیاز نیست، اگرچه این فرآیند در صورت استفاده از تنظیم لیزری باید مطابق ویژگیهای لیزر باشد. با روش تنظیم دقیق جریان بالا، اگر بازدههای قرص نیمه رسانا خوب باشند ممکن است آزمایش در سطح ویفر لازم نباشد. طرح تنظیم دقیق لیزری به پدهای تماسی اضافی نیاز ندارد، اما ساختارهای تنظیمشده با اندازههای مشخصه فرآیند مقیاس نمیگیرند. تنظیم لیزری پیوندها نمیتواند در بستهبندی انجام شود، و به پدهای پروب اضافی برروی قرص نیمه رسانا نیاز دارد. علاوه براین، میتواند به پایههای بستهبندی اضافی برای تنظیمات جریان بالای درون بستهبندی نیاز داشته باشد. مثل شکست زنری، تنظیم پیوند گسسته است. بهبود وضوح به ساختارهای اضافی، افزایش سطح و هزینه نیاز دارد.

تنظیم دقیق EEPROM از حافظه دیجیتالی خاص، غیرفرار برای نگهداری داده تنظیم استفاده میکند. بیتهای داده ذخیرهشده جریانهای اصلاحی را از طریق مبدلهای دیجیتال به آنالوگ (D/A) روی تراشه کنترل میکنند. سلولهای حافظه و مبدلهای دیجیتال به آنالوگ با اندازه مشخصه فرآیند مقیاس میگیرند. تنظیم درون بستهبندی و حتی تنظیم دقیق در سامانه مشتری محتمل است تا جابجاییهای مرتبط با مونتاژ بتوانند کوتاه شوند. اگر بازده منطقی باشد آزمایش در سطح ویفر لازم نیست. برای تنظیم سخت افزار خاصی جز سامانه آزمایشکننده سیگنال مخلوط معمولی لازم نیست، اگرچه ممکن است توسعه نرم افزار آزمایش پیچیدهتر باشد.

از آنجاییکه تنظیمات میتوانند جایگزین شوند، برنامهنویسی مجدد سامانه بطور متناوب برای جبران رانشهای طولانی مدت یا اصلاح ویژگیهای سامانه برای نیازهای جدید امکانپذیر است. تعداد چرخههای برنامهنویسی مجدد محتمل به روندکار بستگی دارد، و محدود است. بیشتر فرآیندهای EEPROM چرخههای بازنویسی کافی برای کنترل باز تنظیم دقیق معمول را فراهم میکنند.

این روش تنظیم نیاز به پردازش خاصی دارد. داده تنظیم ذخیره شده میتوانند تحت شرایط خاص، مخصوصا در دماهای عملیاتی بالا از دست برود. حداقل یک پایه بستهبندی یا پد تماسی دیجیتالی اضافی برای ورود داده تنظیم به حافظه روی تراشه لازم است.

این روش به دلیل الزامات اکسید خیلی نازک تنها در فرآیندهای مبتنی بر MOS در دسترس است. بزرگترین اشکال این است که مبدلهای دیجیتال به آنالوگ روی تراشه بسیار بزرگ هستند، اغلب بزرگتر از مدارهای تقویتکننده که آنها تنظیم میکنند. به همین دلیل، تنظیم EEPROM بیشتر برای مبدل داده یا محصولات سطح سامانه بکاربرده میشود که در آن مبدلهای دیجیتال به آنالوگ تنظیم دقیق درصد بسیار کوچکی از کل سطح قرص نیمهرسانا را نشان میدهند.

شکل 8 ویژگیهای کلیدی هر روش تنظیم دقیق ADI را خلاصه میکند. در این شکل مشاهده میشود که تمام روشهای تنظیم دقیق جایگاه مربوطه خودشان را در تولید عملکرد بالای مدارهای مجتمع خطی دارند.

وضوح | پردازش خاص | AT تنظیمشده | فرآیند |

گسسته | هیچ کدام | ویفر یا آزمایش نهایی | تنظیم دیجیتالی |

پیوسته | مقاومت لایه نازک | ویفر | تنظیم لیزری |

گسسته | هیچ کدام | ویفر | تنظیم حذف زنری |

گسسته | مقاومت لایه نازک یا پلی | ویفر | تنظیم پیوندی |

گسسته | EEPROM | ویفر یا آزمایش نهایی | تنظیم EEPROM |

شکل 8. خلاصه فرآیندهای تنظیم ADI

برای مشاهده سایر نوشتارهای مربوط به الکترونیک و مخابرات، اینجا کلیک کنید!

عالی بود.