فهرست مطالب

نحوه دیباگ کردن برنامه با استفاده از Chipscope

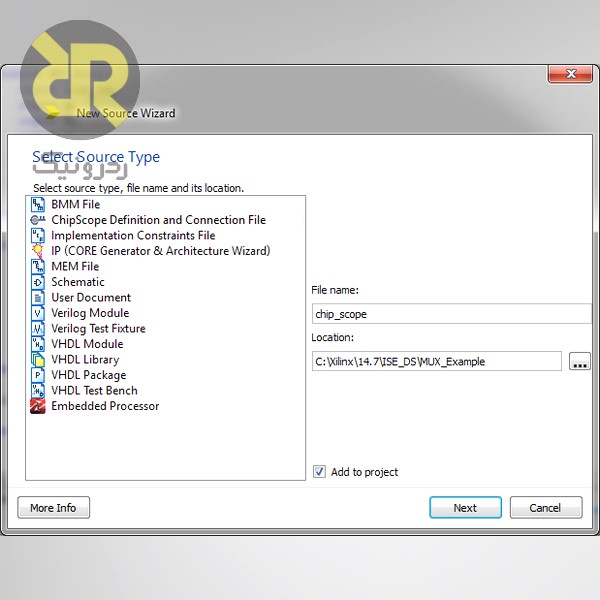

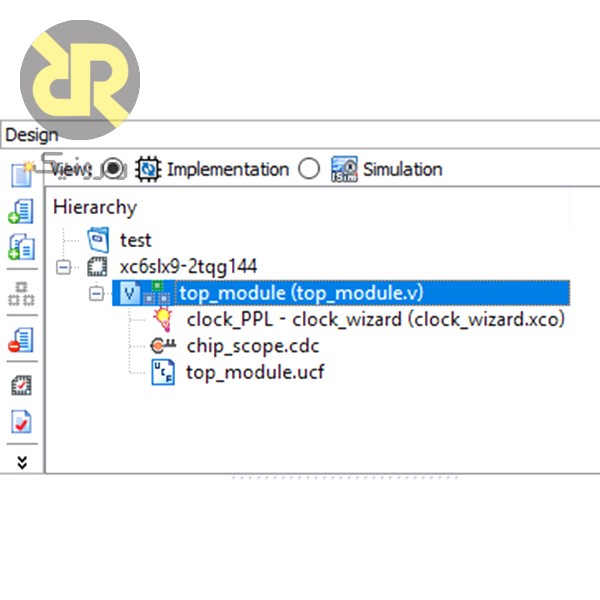

از منوی Project گزینه Add Source را انتخاب کنید. در پنجره باز شده (شکل 28) نوع منبع را ChipScope Definition and Connection File انتخاب کرده و نام و مسیر ذخیره آن را تعیین کنید. سپس بر روی دکمه Next و بعد Finish کلیک کنید. در این مرحله باید Chipscope به پروژه اضافه شده باشد (شکل 29).

انتخاب سیگنالهای موردنظر جهت دیباگ

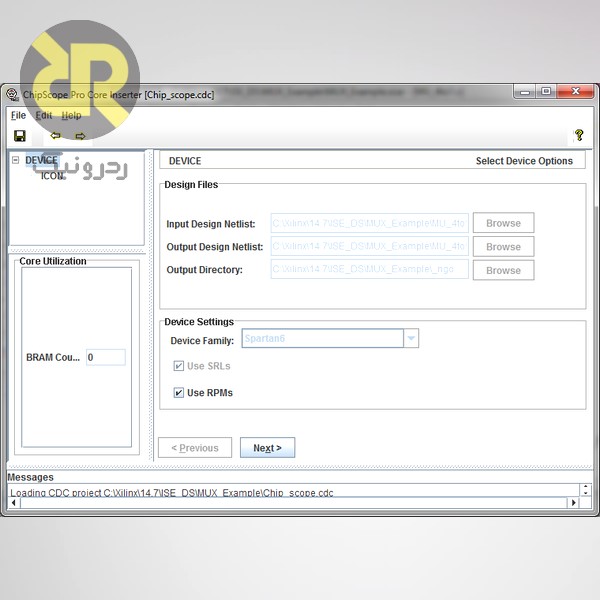

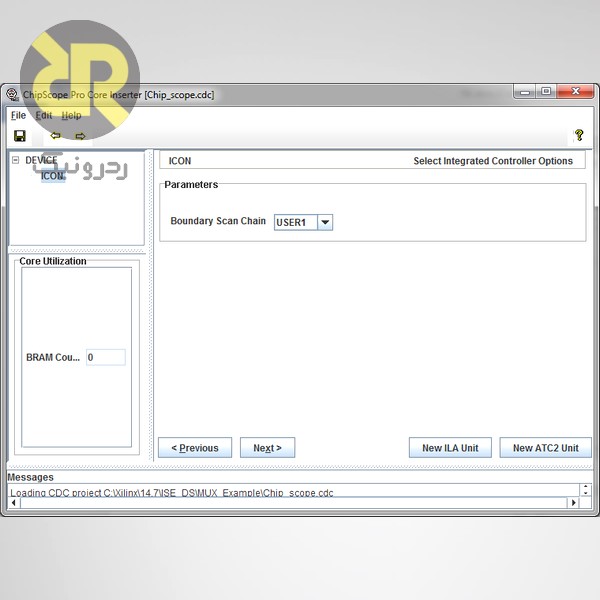

بر روی آیکون Chipscope دو بار کلیک کنید. در صورتیکه خطایی در برنامه وجود نداشته باشد و با موفقیت سنتز شود، پنجره ChipScope Pro Core Inserter (شکل 30) باز میشود. در این پنجره روی دکمه Next کلیک کنید.

در پنجره بعدی (شکل 31) مجدداً روی دکمه Next کلیک کنید.

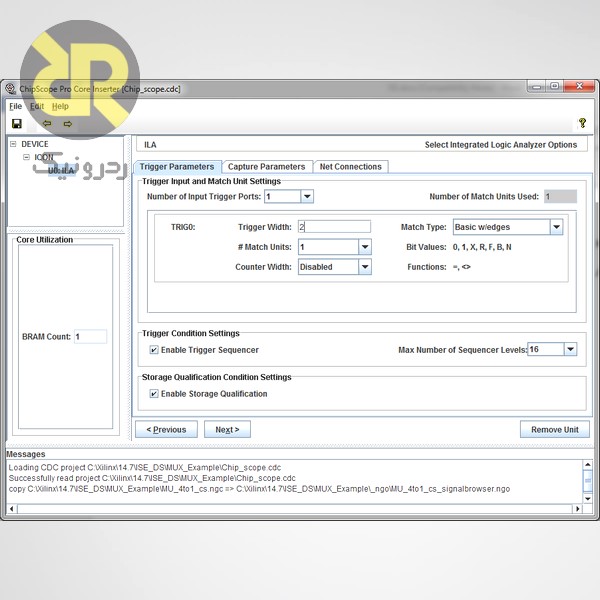

در سربرگ Trigger Parameters (شکل 32) ویژگیها و شرایط تریگ تنظیم میشود. در اینجا تعداد و عرض هر کدام از سیگنالهای تریگر را تنظیم کنید. در اینجا پروژه شرایط تریگر بصورت یک سیگنالهای تریگر دو بیتی تنظیم شده است. بعد از انجام تنظیمات موردنظر بر روی دکمه Next کلیک کنید.

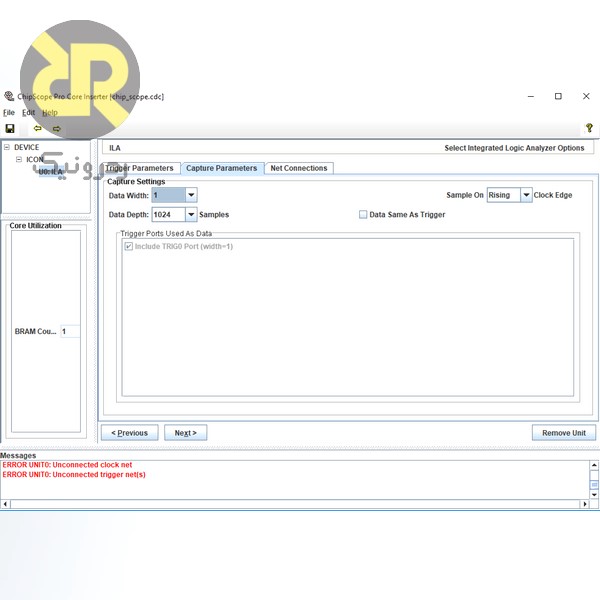

در سربرگ Capture Parameters (شکل 33) تعداد و عمق سیگنالهای موردنیاز برای دیباگ تنظیم میشود. در صورتی که میخواهید سیگنال تریگر با سیگنال داده یکسان باشد، گزینه Data Same As Trigger را فعال کنید. در غیر اینصورت این گزینه را غیرفعال کنید و در فیلد Data Width تعداد سیگنالهای موردنیاز و در فیلد Data Depth عمق آنها را تعیین کنید و سپس بر روی دکمه Next کلیک کنید.

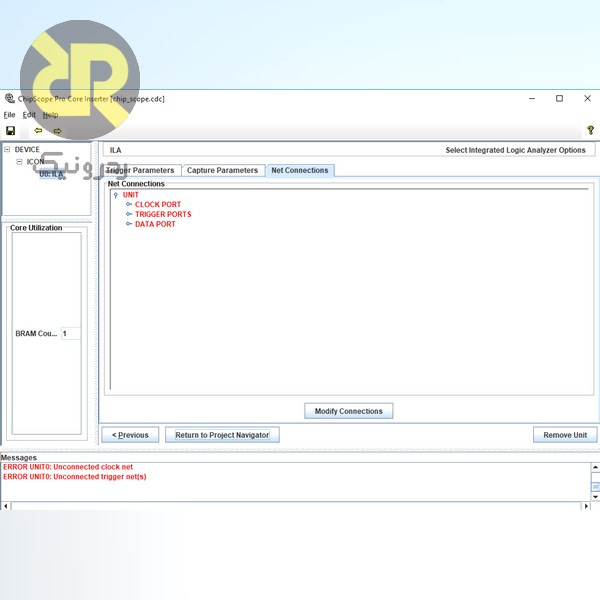

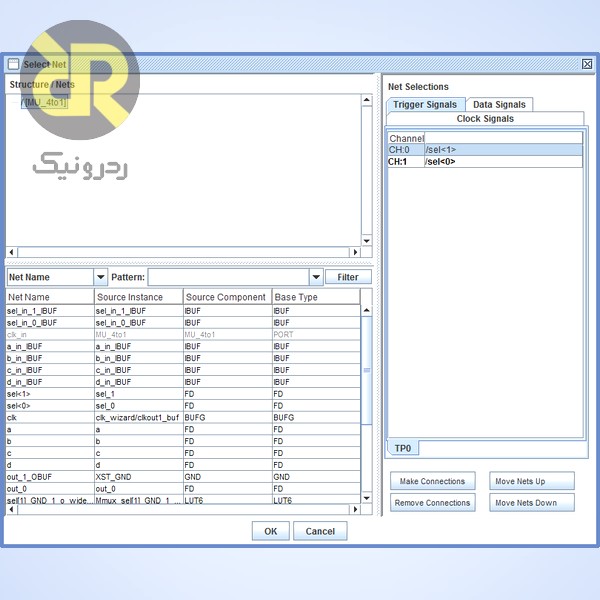

در سربرگ Net Connections (شکل 34) سیگنالهای کلاک، تریگر و داده انتخاب میشوند. بر روی دکمه Modify Connection کلیک کنید تا پنجره Select Net باز شود.

برای اتصال سیگنالهای مدار به پایههای ChipScope ابتدا از منوی Net Selection پایه ChipScope مورد نظر را انتخاب کنید. سپس در منوی سمت راست پایین، از بین سیگنالهای مدار، سیگنال مطلوب را انتخاب نمایید و بر روی دکمه Make Connection کلیک کنید.

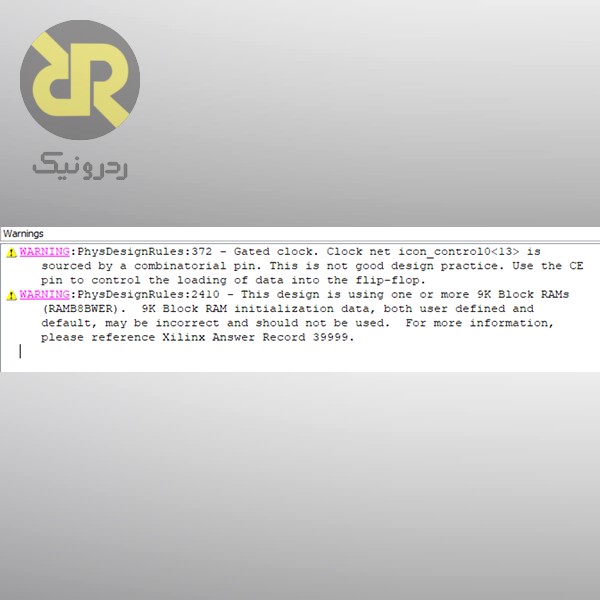

بعد از تعیین کلیه سیگنالها بر روی دکمه OK تا پنجره Select Net بسته شود. سپس Return To Project Navigator کلیک کنید و تغییرات را ذخیره کنید. پروژه را مجدداً Implement کنید و در صورتی که مشکلی روی نداد، Bit Stream را تولید کرده و FPGA را پروگرم کنید. با اضافه کردن ChipScope نرمافزار warning های (شکل 36) را چاپ میکند.

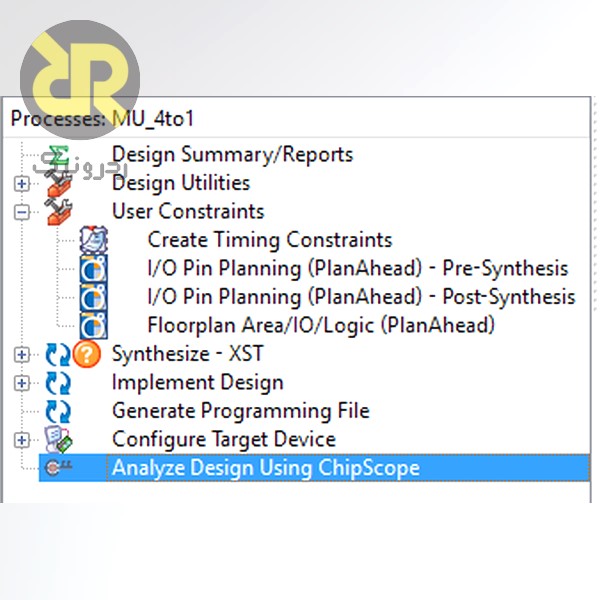

بعد از پروگرم کردن FPGA روی گزینه Analyze Design Using ChipScope (شکل 37) کلیک کنید.

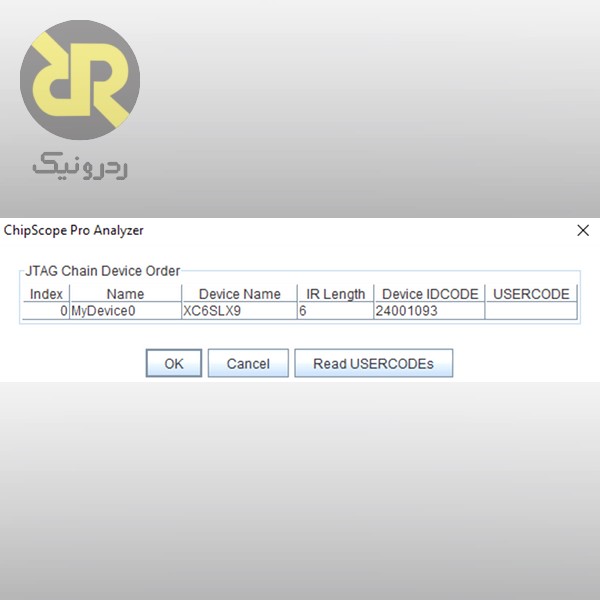

پس از باز شدن نرمافزار ChipScope Pro Analyzer روی آیکون کلیک کنید تا نرمافزار به ChipScope متصل شود. در پنجره باز شده (شکل 38)، دیوایس موردنظر را انتخاب کرده و سپس روی دکمه OK کلیک کنید.

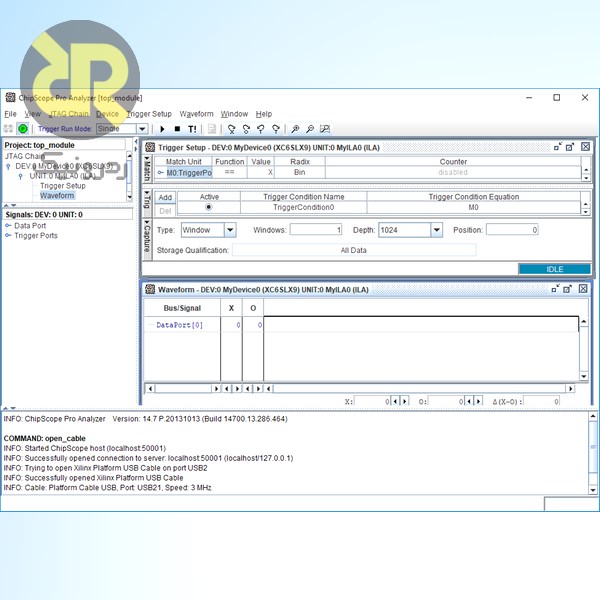

در پنجره ChipScope Pro Analayer (شکل 39) در قسمت Trigger Setup شرایط تریگ تعیین میشود. برای اینکار ابتدا نوع Function و مدار Value را مشخص کنید. بعنوان مثال در صورتی که میخواهید با ”1” شدن سیگنال، تریگ شود باید نوع Function را ”== ” و Value را ”1” قرار دهید. در این نرمافزار میتوان موقعیت شرایط تریگ را مشخص کرد. برای اینکار باید فیلد Position را تنظیم کرد. بعنوان مثال اگر بخواهیم سیگنال های داده را 500 نمونه قبل از تریگ شدن ببینیم باید مقدار فیللد Position را روی 500 تنظیم کرد.

در قسمت Waveform سیگنالهای داده نشان داده میشود. با کلیک بر روی نوار ابزار Chipscope شروع به کار میکند و به محض ایجاد شرایط تریگر، سیگنالهای داده را نمایش میدهد. برای متوقف کردن ChipScope میتوان بر روی گزینه stop کلیک کرد. گزینه T سیگنالهای داده را بدون ایجاد شرایط تریگر نمایش میدهد.